#### EC 3451/ LINEAR INTEGRATED CIRCUITS

#### <u>UNIT I</u>

#### **BASICS OF OPERATIONAL AMPLIFIERS**

#### Syllabus:

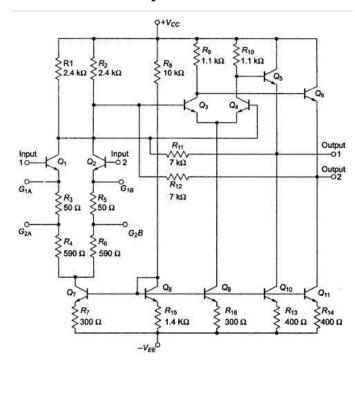

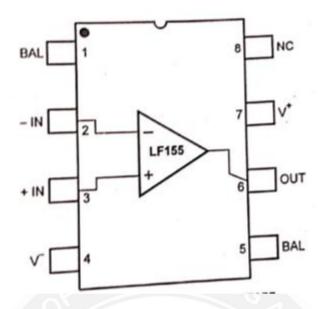

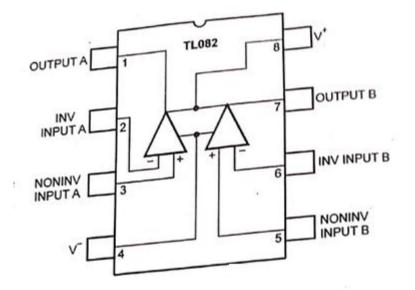

Current mirror and current sources, Current sources as active loads, Voltage sources, Voltage References, BJT Differential amplifier with active loads, Basic information about op-amps – Ideal Operational Amplifier - General operational amplifier stages - and internal circuit diagrams of IC 741, DC and AC performance characteristics, slew rate, Open and closed loop configurations, JFET operational amplifiers-LF 155 and TL082.

#### **1.1. CURRENT MIRROR (CONSTANT CURRENT SOURCE)**

Q1. Draw and explain the circuit diagram of a basic current mirror. [Nov 003]

Q2. Explain the working of constant current source with a circuit diagram. [May 2005, Nov 006] Q3. Draw the circuit of simple bipolar transistor current source and show that its output current is dependent on the β of the transistor. [May 2007, Nov 2009]

#### **Definition:**

A circuit in which the output current is equal to input current is called **current mirror**. In current mirror circuit, the output current is the mirror image of the input current.

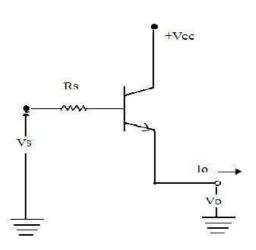

# **Circuit Diagram:**

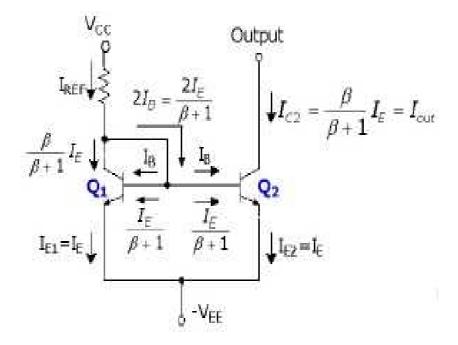

Fig. Current mirror circuit

#### **Explanation:**

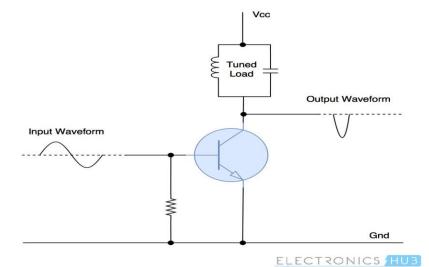

- $\checkmark$  A constant current source uses the transistor in the active mode of operation.

- ✓ The collector current is independent of the collector voltage.

- ✓ Transistors  $Q_1$ & $Q_2$  are matched.

- ✓ The circuit is fabricated using IC technology.

- ✓ Base and emitter of  $Q_1$  &  $Q_2$  are tied together and have the same VBE.

- ✓ Since  $Q_2$  is identical to  $Q_1$ , the emitter current of  $Q_2$  will be equal to emitter current of  $Q_1$  which is approximately equal to I<sub>ref</sub>.

- ✓ Aslong as Q₂ is maintained in the active region, its collector current IC₂=Iout will be approximately equal to Iref.

- ✓ Since the output current Io is a reflection or mirror of the reference current I<sub>ref</sub>, the circuit is often referred to as a current mirror.

#### Analysis:

✓ If the effect of finite β is considered, this may lead to an output current not equal to the input reference current, since

where the expression for IREF is found by using KCL at the collector of Q1.

$\checkmark$  The current gain of the current mirror is

$$\frac{I_{out}}{I_{REF}} = \frac{\beta}{\beta + 2}$$

which approaches unity for  $\beta$  very large.

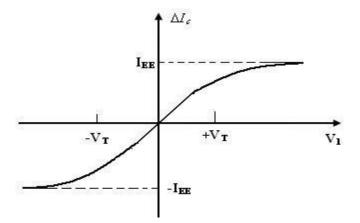

#### Current source output current characteristics

#### **Disadvantage:**

The output resistance of the current mirror is limited by the r<sub>o</sub> of Q<sub>2</sub>,

$$\Gamma_o = \frac{V_A}{I_{out}} \approx \frac{V_A}{I_{REF}} \,.$$

## **1.2 CURRENT SOURCES**

#### **Current Source:**

#### **Definition:**

A circuit which generates current is known as current source.

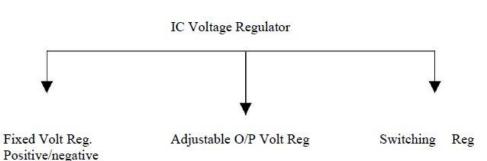

#### **Types of current sources:**

- 1. Widlar current source

- 2. Wilson current source

## **<u>1. Widlar Current Source</u>**

Q. Draw the circuit of widlar current source and derive an expression for its output current. [May 2006, Nov 2007, May 2008, Nov 2008]

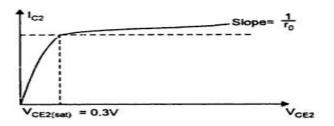

#### **Circuit Diagram:**

#### Explanation:

- $\checkmark$  In the Widlar current source, resistor (R<sub>2</sub>) is added to the emitter circuit of transistor Q<sub>2</sub>.

- $\checkmark$  Since multistage amplifier systems have high gain, bias currents must be small.

- ✓ The Widlar current source generates small constant currents using relatively small resistors.

#### Analysis:

$$I_{C} = I_{o}e^{\left(\frac{V_{BE}}{V_{T}}\right)},$$

$\blacktriangleright$  Where, Io is the reverse saturation current,

> VT is the thermal voltage ( $kT/q\approx 26mV$  at room temperature) Solving Equation for VBE, we get

$$V_{BE} = V_T \ln \left( \frac{I_C}{I_O} \right).$$

✓ We can express VBE1 and VBE2 in the circuit as,

$$V_{BE1} = V_T \ln \left( \frac{I_{C1}}{I_0} \right) \cong V_T \ln \left( \frac{I_{REF}}{I_0} \right); \quad V_{BE2} = V_T \ln \left( \frac{I_{C2}}{I_0} \right) = V_T \ln \left( \frac{I_{out}}{I_0} \right).$$

✓ Assuming we have matched devices,  $V_T$  and  $I_O$  are the same for  $Q_1$  and  $Q_2$ .

✓ Subtracting VBE2 from VBE1, and using the appropriate property of logarithms (i.e., lnA-lnB=ln(A/B)),

$$V_{BE1} - V_{BE2} = V_T \ln \left( \frac{I_{REF}}{I_{out}} \right).$$

✓ Writing a KVL around the base loop of the two transistors,

$$V_{BE1} = V_{BE2} + I_{E2}R_2$$

; or  $V_{BE1} - V_{BE2} = I_{E2}R_2$

✓ Assuming that IC<sub>2</sub>=IE<sub>2</sub>=Iout, and using our expression for  $V_{BE1}$ - $V_{BE2}$ ,

$$I_{out}R_2 = V_7 \ln \left(\frac{I_{REF}}{I_{out}}\right).$$

✓ Since  $I_{REF}$  (=IC<sub>1</sub>) is usually defined in design can be solved for the required value of R<sub>2</sub>.

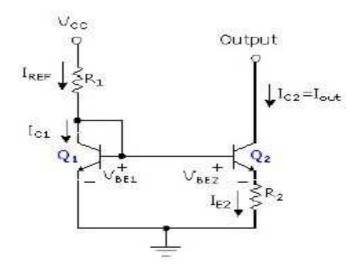

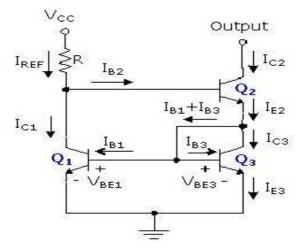

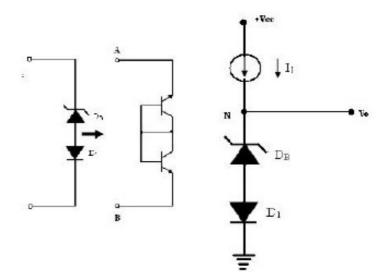

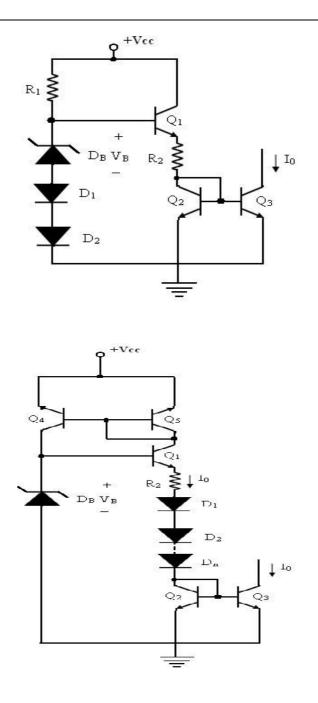

# 2. Wilson Current Source

# Q. With neat diagram explain Wilson current source. [Nov 2009] <u>Circuit Diagram</u>

## **Explanation:**

- Another current source configuration that possesses increased output resistance is the Wilson current source.

- $\checkmark$  The increased r<sub>o</sub> of the Wilson current source is due to the negative feedback provided by Q<sub>3</sub>.

- ✓ It provides an output current Io which is very nearly equal to  $V_{ref}$  and also exhibits a very high output resistance.

#### Analysis:

$\checkmark$  Writing a KCL equation at the emitter of Q2

$$I_{E2} = I_{C3} + I_{B1} + I_{B3}$$

.

- ✓ If all three transistors are matched  $V_{BE1}=V_{BE2}=V_{BE3}$ ,  $\beta_1=\beta_2=\beta_3$ ,  $I_{B1}=I_{B3}$ , and  $I_{C1}=I_{C3}$ .

- ✓ Tthe relationship between base and collector currents ( $I_B=I_C/\beta$ ).

- $\checkmark$  We can rewrite the expression for I<sub>E2</sub> as

$$I_{E2} = I_{C3} \left( 1 + \frac{2}{\beta} \right).$$

✓ Using  $I_{C2}=\alpha I_{E2}=\beta I_{E2}/(\beta+1)$  and simplifying,

$$I_{C2} = \frac{I_{C3}(1+2/\beta)\beta}{\beta+1} = \frac{I_{C3}(\beta+2)}{(\beta+1)}.$$

✓ Now, if we sum the currents at the base of  $Q_2$ ,

$$I_{C1} = I_{C3} = I_{REF} - I_{B2} = I_{REF} - I_{C2} / \beta.$$

✓ Solving for  $I_{C2}$ , we get an expression for the output current ( $I_{C2}$ ) in terms of the transistor parameter  $\beta$  and the input current,  $I_{REF}$

$$I_{C2} = \frac{\beta^2 + 2\beta}{\beta^2 + 2\beta + 2} I_{REF} = \left(1 - \frac{2}{\beta^2 + 2\beta + 2}\right) I_{REF}$$

- ✓ For reasonable values of  $\beta$ , the second term will be negligible and I<sub>C2</sub>=I<sub>out</sub>=I<sub>REF</sub>.

- ✓ Therefore, in addition to the increased output resistance, the Wilson configuration provides an output that is almost independent of the internal transistor characteristics.

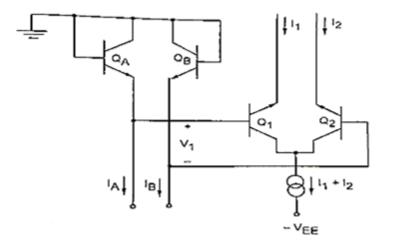

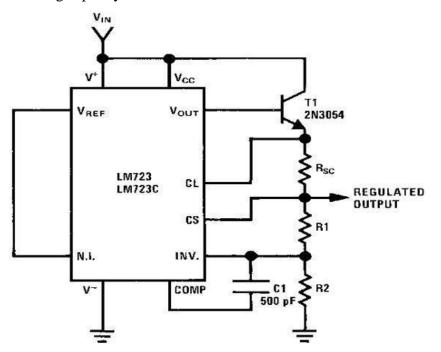

# **1.3. CURRENT SOURCES AS ACTIVE LOADS**

- $\checkmark$  The current source can be used as an active load in both analog and digital IC's.

- The active load realized using current source in place of the passive load (i.e. a resistor) in the collector arm of differential amplifier.

- ✓ The active load used to achieve high voltage gain without requiring large power supply voltage.

#### **<u>1.4. VOLTAGE SOURCES</u>**

# Q. Explain the voltage sources with neat circuit diagram. <u>Definition:</u>

A voltage source is a circuit that produces an output voltage  $V_0$ , which is independent of the load.

## Methods:

There are four methods used to produce a voltage source, namely,

- 1. Voltage source circuit using Impedance transformation:

- 2. Emitter-follower or Common Collector Type Voltage source:

- 3. Voltage source using breakdown voltage of the base- emitter junction

- 4. Voltage Source using VBE as a reference:

#### 1. Voltage source circuit using Impedance transformation:

#### **Circuit Diagram:**

#### **Explanation:**

- $\checkmark$  The voltage source circuit using the impedance transforming property of the transistor is shown in figure.

- $\checkmark$  The source voltage Vs drives the base of the transistor through a series resistance R<sub>S</sub>.

- $\checkmark$  The output is taken across the emitter.

- $\checkmark$  From the circuit, the output ac resistance looking into emitter is given by

$$R_0 = \frac{R_s}{\beta + 1} + r_{eb}$$

; With  $\beta >> 100$ ,  $R_0 = \frac{R_s}{\beta + 1}$

- $\checkmark$  Equation is applicable only for small changes in the output current.

- $\checkmark$  The load regulation parameter indicates the changes in V\_o resulting from large changes in output current I\_o.

- ✓ Reduction in V₀ occurs as Io goes from no-load current to full-load current and this factor determines the output impedance of the voltage sources.

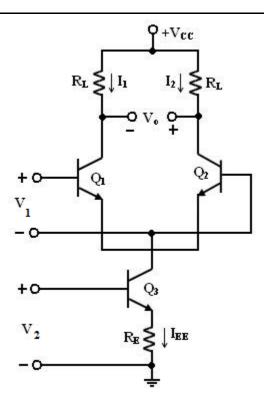

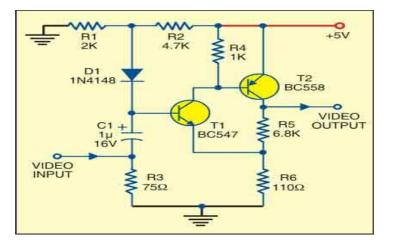

# 2.<u>Emitter– follower or Common Collector Type Voltage source:</u> Circuit Diagram:

# **Explanation:**

- $\checkmark$  The figure shows an emitter follower or common collector type voltage source.

- $\checkmark$  This voltage source is suitable for the differential gain stage used in op-amps.

- ✓ The low output impedance of the common-collector stage simulates a low impedance voltage source with an output voltage level of Vo represented by

$$V_0 = V_{CC} \frac{R_2}{R_1 + R_2}$$

- $\checkmark$  The diode  $D_1$  is used for offsetting the effect of dc value  $V_{BE}$  , across the E-B junction of the transistor.

- ✓ For compensating the temperature dependence of  $V_{BE}$  drop of Q1.

- ✓ The load  $Z_L$  shown in dotted line represents the circuit biased by the current through  $Q_1$ .

The impedance  $R_0$  looking into the emitter of  $Q_1$  derived from the hybrid  $\pi$  model is given by

- ✓ The voltage source using common collector stage has the limitations of its weakness for changes in bias voltage V<sub>N</sub>.

- ✓ The output voltage  $V_o$  with respect to changes in supply voltage Vcc.

- $\checkmark$  This is overcome in the voltage source circuit using the breakdown voltage of the base- emitter junction.

- ✓ The emitter follower stage of common collector is eliminated in this circuit, since the impedance seen looking into the bias terminal N is very low.

- $\checkmark$  The current source I<sub>1</sub> is normally simulated by a resistor connected between Vcc and node n.

- ✓ Then, the output voltage level  $V_0$  at node N is given by  $V0 = V_B + V_{BE}$  Where  $V_B$  is the breakdown voltage of diode  $D_B$  and  $V_{BE}$  is the diode drop across  $D_1$ .

- $\checkmark$  The breakdown diode D<sub>B</sub> is normally realized using the base-emitter junction of the transistor.

- $\checkmark$  The diode D<sub>1</sub> provides partial compensation for the positive temperature coefficient effect of V<sub>B</sub>.

- ✓ In a monolithic IC structure,  $D_B$  and  $D_1$  can be conveniently realized as a single transistor with two individual emitters as shown in figure.

#### Advantages:

- 1. Producing low ac impedance and

- 2. Resulting in effective decoupling of adjacent gain stages.

#### 3. Voltage source using breakdown voltage of the base- emitter junction

- $\checkmark$  The structure consists of composite connection of two transistors which are diode connected back-to back.

- ✓ Since the transistors have their base to collector terminals common, they can be designed as a single transistor with two emitters.

$\checkmark$  The output resistance R<sub>0</sub> looking into the output terminal in figure is given by

Ro=R<sub>B</sub>+V<sub>T</sub>/ I<sub>1</sub>

- ✓ where  $R_B$  and  $V_T$  /  $I_1$  are the ac resistances of the base–emitter resistance of diode  $D_B$  and  $D_1$  respectively.

- ✓ Typically,  $R_B$  is in the range of 40Ω to 100Ω, and  $V_0$  in the range of 6.5V to 9V.

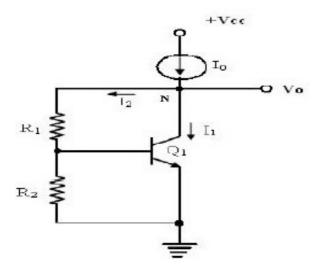

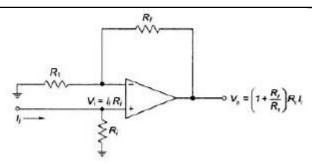

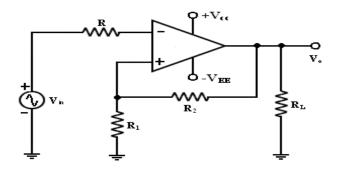

#### **4.Voltage Source using VBE as a reference:**

- ✓ The output stage of op-amp requires stabilized bias voltage source, which can be obtained using a forward-biased diode connected transistor.

- ✓ The forward voltage drop for such a connection is approximately 0.7V, and it changes slightly with current.

- ✓ When a voltage level greater than 0.7V, is needed, several diodes can be connected in series, which can offer integral multiples of 0.7V.

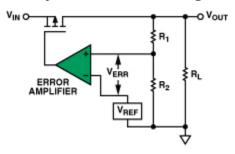

- ✓ Alternatively, the figure shows a multiplier circuit, which can offer voltage levels that need not be integral multiplied of 0.7V.

- ✓ The drop across R2 equals VBE drop of Q1. Considering negligible base current for Q1, current through R2 is the same as that flowing through R1.

- $\checkmark$  Therefore, the output voltage V<sub>0</sub> can be expressed as

$$V_0 = I_2(R_1 + R_2) = \frac{V_{BE}}{R_2}(R_1 + R_2) = V_{BE}(\frac{R_1}{R_2} + 1)$$

- ✓ Hence, the voltage  $V_0$  can be any multiple of  $V_{BE}$  by properly selecting the resistors  $R_1$  and  $R_2$ .

- ✓ Due to the shunt feedback provided by  $R_1$ , the transistor current  $I_1$  automatically adjusts itself, towards maintaining  $I_2$  and  $V_0$  relatively independent of the changes in supply voltage.

$\checkmark$  The ac output resistance of the circuit R<sub>0</sub> is given by,

$$R_{O} = \frac{dV_{0}}{dI_{O}} = \frac{R_{1} + R_{2}}{1 + g_{m}R_{2}} \approx \frac{(R_{1} + R_{2})}{R_{2}g_{m}} \text{ When } g_{m}R_{2} >>1$$

$$R_{O} = \frac{V_{0}}{V_{BE}} \frac{1}{g_{m}} = \frac{V_{O}}{V_{BE}} \frac{V_{1}}{I_{C}} \text{ as } \frac{V_{O}}{V_{BE}} = \frac{(R_{1} + R_{2})}{R_{2}}$$

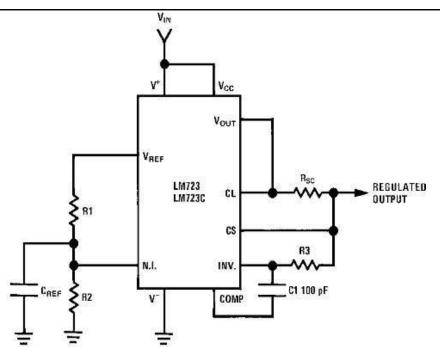

#### 1.5. Voltage References

#### Q. Explain the voltage references with neat circuit diagram.

#### **Definition:**

✓ The circuit that is designed for providing a constant voltage independent of changes in temperature is called a voltage reference.

#### **Concepts:**

✓ The most important characteristic of a voltage reference is the temperature coefficient reference voltage TCR, and it is expressed as

$$T_{CR} = \frac{dV_R}{dT}$$

- $\checkmark$  Reference voltage must be independent of any temperature change.

- ✓ Reference voltage must have good power supply rejection which is as independent of the supply voltage.

- $\checkmark$  Output voltage must be as independent of the loading of output current.

- $\checkmark$  The circuit should have low output impedance.

- ✓ The voltage reference circuit is used to bias the voltage source circuit, and the combination can be called as the voltage regulator.

- ✓ The basic design strategy is producing a zero TCR at a given temperature, and thereby achieving good thermal ability.

- ✓ Temperature stability of the order of 100 ppm/<sup>0</sup>C is typically expected.

#### Methods:

There are two methods.

- 1. Voltage Reference circuit using Avalanche Diode Reference:

- 2. Voltage Reference circuit using temperature compensation scheme

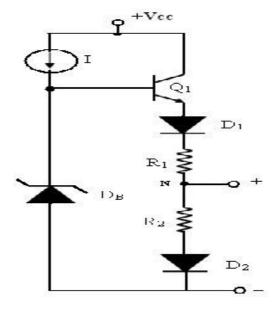

## 1. Voltage Reference circuit using temperature compensation scheme:

# Circuit Diagram:

# **Explanation:**

- $\checkmark$  This design utilizes the close thermal coupling achievable among the monolithic components.

- This technique compensates the known thermal drifts by introducing an opposing and compensating drift source of equal magnitude.

- ✓ A constant current I is supplied to the avalanche diode  $D_B$  and it provides a bias voltage of  $V_{B to}$  the base of  $Q_1$ .

- ✓ The temperature dependence of the  $V_{BE}$  drop across  $Q_1$  and those across  $D_{1 \text{ and }} D_2$  results in respective temperature coefficients.

- ✓ Hence, with the use of resistors  $R_1$  and  $R_2$  with tapping across them at point N compensates for the temperature drifts in the base- emitter loop of  $Q_1$ .

- $\checkmark$  This results in generating a voltage reference V<sub>R</sub> with normally zero temperature coefficient.

- 2. Voltage Reference circuit using Avalanche Diode Reference:

# **Circuit Diagram**

#### **Explanation:**

- ✓ A voltage reference can be implemented using the breakdown phenomenon condition of a heavily doped PN junction.

- $\checkmark$  The Zener breakdown is the main mechanism for junctions, which breakdown at a voltage of 5V or less.

- $\checkmark$  For integrated transistors, the base-emitter breakdown voltage falls in the range of 6 to 8V.

- Therefore, the breakdown in the junctions of the integrated transistor is primarily due to avalanche multiplication.

- ✓ The avalanche breakdown voltage  $V_B$  of a transistor incurs a positive temperature coefficient, typically in the range of 2mV/0 C to 5mV/<sup>0</sup>C.

- ✓ The base bias for transistor Q1 is provided through register R1 and it also provides the dc current needed to bias DB, D1 and D2.

- ✓ The voltage at the base of Q1 is equal to the Zener voltage VB added with two diode drops due to D1 and D2.

- ✓ The voltage across  $R_2$  is equal to the voltage at the base of  $Q_1$  less the sum of the base emitter voltages of  $Q_1$  and  $Q_2$ .

- ✓ Hence, the voltage across R2 is approximately equal to that across DB = VB. Since Q2 and Q3 act as a current mirror circuit, current I<sub>0</sub> equals the current through R2.

$$I_O = \frac{V_B}{R_2}$$

- ✓ It shows that, the output current Io has low temperature coefficient, if the temperature coefficient of R2 is low, such as that produced by a diffused resistor in IC fabrication.

- ✓ The zero temperature coefficients for output current can be achieved, if diodes are added in series with R2, so that they can compensate for the temperature variation of R2 and  $V_B$ .

- $\checkmark$  The temperature compensated avalanche diode reference source circuit is shown in figure.

- ✓ The transistor Q4 and Q5 form an active load current mirror circuit. The base voltage of Q1 is the voltage VB across Zener DB.

- ✓ Then, VB = (VBE \* n) +VBE across Q1 + VBE across Q2 + drop across R2. Here, n is the number of diodes.

- $\checkmark$  It can be expressed as

$$V_B = (n+2) V_{BE+10} * R_2$$

$\checkmark$  Differentiating for V<sub>B</sub>, I<sub>0</sub>, R2 and VBE partially, with respect to temperature T, we get

$$\frac{\partial V_B}{\partial T} = n + 2\frac{\partial V_{BE}}{\partial T} + R_2\frac{\partial I_0}{\partial T} + I_0\frac{\partial R_2}{\partial T}$$

$\checkmark$  Dividing throughout by I0 R2, we get

$$\frac{l}{l_0}\frac{\partial I_0}{\partial T} = 0 = \frac{1}{R_2 I_0} \left[\frac{\partial V_B}{\partial T} - (n+2)\frac{\partial V_{BE}}{\partial T} - \frac{1}{R_2}\frac{\partial R_2}{\partial T}\right]$$

✓ Therefore, zero temperature coefficient of IO can be obtained, if the above condition is satisfied.

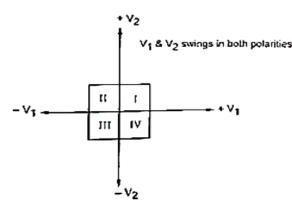

# **1.6. DIFFERENTIAL AMPLIFIER**

# Q.Explain the operation of basic differential amplifier. [May 2005]

# **Definition:**

An amplifier that is used to amplify the difference between two signals is known as **differential amplifier.**

- $\checkmark$  This forms the basic input stage of an integrated amplifier.

- $\checkmark$  The basic differential amplifier has the following important properties.

- 1. Excellent stability

- 2. High versatility and

- 3. High immunity to interference signals

## **Advantages**

- 1. Lower cost

- 2. Easier fabrication as IC component and closely matched components.

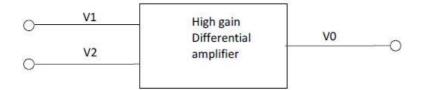

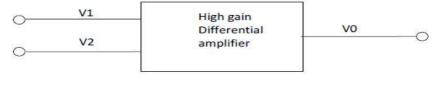

# **Block Diagram:**

- ✓ The above figure shows the basic block diagram of a differential amplifier, with two input terminals and one output terminal.

- ✓ The output signal of the differential amplifier is proportional to the difference between the two input signals. V0 = Adm (V1 V2)

- ✓ If V1 = V2, then the output voltage is zero.

- $\checkmark$  A non-zero output voltage V0 is obtained when V1 and V2 are not equal.

- ✓ The difference mode input voltage is defined as Vm = V1 V2

- $\checkmark$  The common mode input voltage is defined as

$$V_{CM} = \frac{V_{1+V2}}{2}$$

✓ If V1 = V2, then the differential mode input signal is zero and common mode input signal is Vcm = V1 = V2.

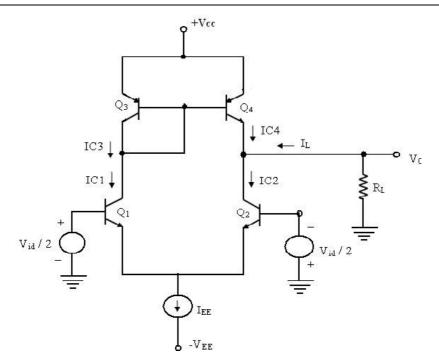

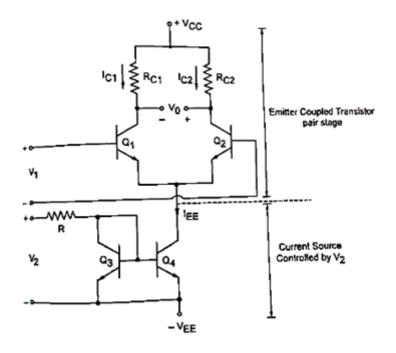

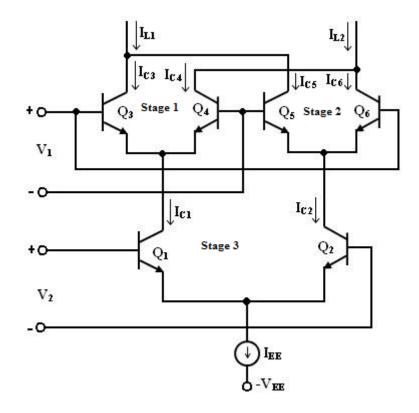

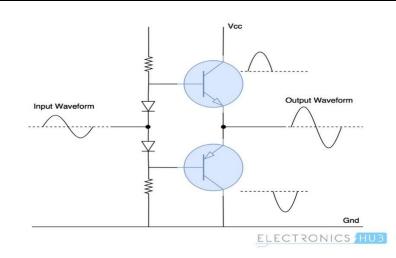

# **1.6.1. DIFFERENTIAL AMPLIFIER WITH ACTIVE LOAD:**

Q.Draw the circuit of a differential amplifier with current mirror load. Drive an expression for its gain. (May 2007, Dec 2018, May 2018) [Nov/Dec 2022]

- ✓ Differential amplifier is designed with active loads to increase the differential mode voltage gain.

- $\checkmark$  The open circuit voltage gain of an op-amp is needed to be as large as possible.

- $\checkmark$  This is got by cascading the gain stages which increase the phase shift.

- $\checkmark$  The gain can be increased by using large values of collector resistance.

- $\checkmark$  For such a circuit, the voltage gain is given by Adm = gm Rc

- $\checkmark$  To increase the gain the Ic Rc product must be made very large.

#### **Limitations in IC fabrication**

- 1. A large value of resistance needs a large chip area.

- 2. For large RC, the quiescent drop across the resistor increased.

- 3. A large power supply will be required to maintain a given operating current.

- 4. Large monolithic resistor introduces large parasitic capacitances which limits the frequency response of the amplifier.

- 5. For linear operation of the differential pair, the devices should not be allowed to enter into saturation.

- ✓ This limits the max input voltage that can be applied to the bases of transistors Q1 and Q2 the basecollector junction must be allowed to become forward-biased by more than 0.5V.

- ✓ The large value of load resistance produces a large dc voltage drop (IEE / 2) Rc, so that the collector voltage will be VC=Vcc (IEE/2) RC and it will be substantially less than the supply voltage Vcc.

- $\checkmark$  This will reduce the input voltage range of the differential amplifier.

- $\checkmark$  Due to the reasons cited above, an active load is preferred in the differential amplifier configurations.

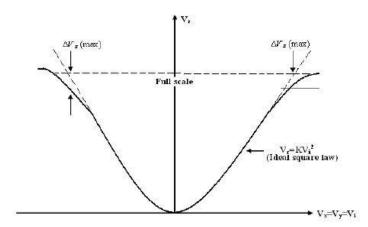

#### BJT Differential Amplifier using active loads:

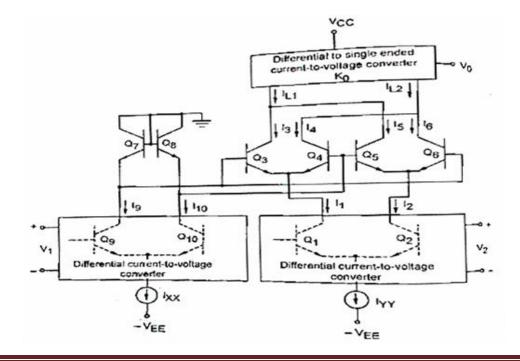

✓ A simple active load circuit for a differential amplifier is the current mirror active load as shown in figure.

- ✓ The active load comprises of transistors Q3 and Q4 with the transistor Q3 connected as a Diode with its base and collector shorted. The circuit is shown to drive a load RL.

- ✓ When an ac input voltage is applied to the differential amplifier, the various currents of the circuit are given by IC4 = IC3 = IC1 = gmVid/2, where IC4 = IC3 due to current mirror action. IC2 = -gmVid/2.

- $\checkmark$  We know that the load current IL entering the next stage is

IL= IC2-IC4 = - gmVid/2 - gmVid/2 = - gmVid

- ✓ Then, the output voltage from the differential amplifier is given by V0= ILRL =  $g_m R_L V_{id}$ .

- $\checkmark$  The ac voltage gain of the circuit is given by

$$A_V = \frac{v_0}{v_{id}} = g_{mR_L}$$

- $\checkmark$  The amplifier can amplify the differential input signals

- ✓ It provides single-ended output with a ground reference since the load RL is connected to only one output terminal.

- $\checkmark$  This is made possible by the use of the current mirror active load.

- ✓ The output resistance Ro of the circuit is that offered by the parallel combination of transistors Q2 (NPN) and Q4 (PNP). It is given by  $Rr = ro2 \parallel ro4$

#### Analysis of BJT differential amplifier with active load:

✓ The collector currents of all the transistors are equal. IC1 = IC2 = IC3 = IC4 = IEE/2.

$\checkmark$  The Collector -emitter voltages of Q1 and Q2 are given by

VCE1-VCE2 =VC-VE=V CC - VEB-(-VEB)= VCC

- $\checkmark$  Equation shows that, the offset is higher than that of a resistive loaded differential amplifier A.

- ✓ This can be reduced by the use of emitter resistors for Q 3 and Q 4, and a transistor Q5 in the current mirror load.

#### Common Mode Rejection Ratio (CMRR)

- $\checkmark$  CMRR is defined as the ratio of differential mode gain to the common mode gain.

- ✓ The common mode rejection ratio is a measure of the differential amplifier's ability to reject the common mode signal and amplify the differential mode signal.

$$\text{CMRR} = \left| \frac{A_{dm}}{A_{cm}} \right| = \left| \frac{v_{o1}/v_{id}}{v_{o1}/v_{ic}} \right| = \frac{\frac{g_{m1}R_C}{2}}{\frac{\beta_{o1}R_C}{r_{\pi 1} + (1 + \beta_{o1})2R_{EE}}} \approx g_{m1}R_{EE} = \frac{I_{EE}R_{EE}}{2V_t}$$

✓ Thus, the larger the input trans conductance or REE, the larger the common mode rejection ratio.

## Input common-mode range (ICMR)

The **input common-mode range** is the range of common-mode voltages over which the differential amplifier continues to sense and amplify the difference signal with the same gain.

Typically, the ICMR is defined by the common-mode voltage range over which all MOSFETs remain in the saturation region and all BJTs remain in the active region.

#### Output offset voltage (VOS(out))

The **output offset voltage** is the voltage which appears at the output of the differential amplifier when the input terminals are connected together.

#### <u>Input offset voltage (VOS(in) = VOS)</u>

The input offset voltage is equal to the output offset voltage divided by the differential voltage gain.

$$V_{OS} = \frac{V_{OS}(\text{out})}{A_{VD}}$$

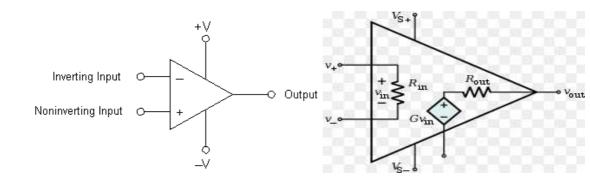

# **1.7.BASIC INFORMATION ABOUT OPERATIONAL AMPLIFIERS**

## Q. Explain about Ideal Op-amp in detail. [May 2018)

- $\checkmark$  An operational amplifier is a direct coupled high gain amplifier.

- ✓ It consists of one or more differential amplifiers, followed by a level translator and an output stage.

- $\checkmark$  It is a versatile device.

✓ It is used to amplify ac as well as dc input signals & designed for computing mathematical functions such as addition, subtraction, multiplication, integration & differentiation.

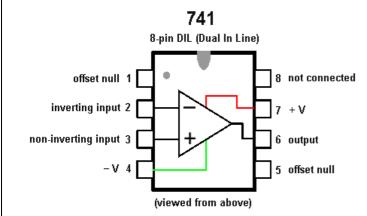

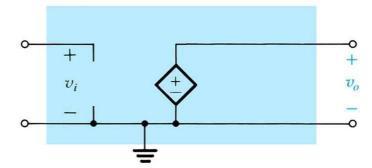

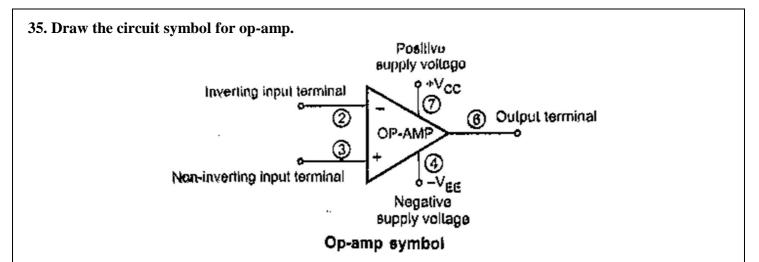

# Symbol:

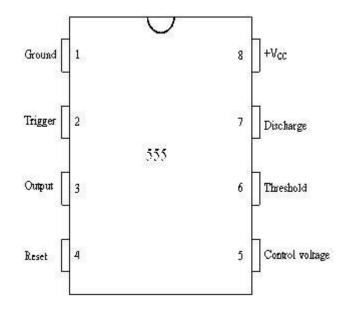

# **Pin Configuration:**

# Ideal characteristics of OPAMP

- 1. Open loop gain infinite

- 2. Input impedance infinite

- 3. Output impedance zero

- 4. Bandwidth infinite

- 5. Zero offset, ie, Vo=0 when V1=V2=0

# **Ideal Vs Practical Op-Amp**

| Parameter                       | Ideal | Practical       |

|---------------------------------|-------|-----------------|

| Open Loop gain A                | ~     | 10 <sup>5</sup> |

| Bandwidth <i>BW</i>             | œ     | 10-100Hz        |

| Input Impedance Z <sub>in</sub> | ×     | >1MΩ            |

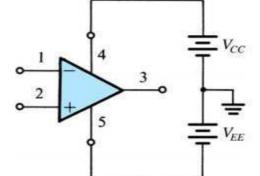

Op amp with dc power supplies

| Output Impedance Z <sub>out</sub> | 0 Ω                                                              | 10-100 Ω                                                                      |

|-----------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Output Voltage V <sub>out</sub>   | Depends only on<br>$V_d = (V_+ - V)$ Differential mode<br>signal | Depends slightly on<br>average input $V_c = (V_++V)/2$<br>Common- Mode signal |

| CMRR                              | ×                                                                | 10-100dB                                                                      |

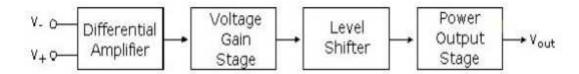

# **1.8. GENERAL OPERATIONAL AMPLIFIER STAGES**

## Q1. Explain the general stages of op-amp with block diagram.

Q2. Draw and explain the block diagram of an op amp. Discuss the functions of each stage in detail.[Nov/Dec 2021] [Nov/Dec 2022]

## 1. Input stage:

✓ The input stage, or **differential amplifier**, provides the common-mode rejection to op-amp operation.

- $\checkmark$  It also supplies the large input impedance.

- $\checkmark$  It allows coupling to a high impedance source without loss of signal level.

- ✓ The differential amplifier may also provide voltage gain if the output of the differential amplifier is connected to an emitter follower with a large emitter resistor.

- ✓ The Emitter Follower amplifier will provide a high impedance load to the differential amplifier to obtain a high voltage gain.

# 2. Intermediate stage:

- ✓ The intermediate stages are shown as the **voltage gain stage and the level shifter** in the figure above.

- ✓ The voltage gain stage usually consists of one or more CE amplifiers to provide the bulk of the overall voltage gain.

- ✓ Linear operational amplifiers are direct coupled to eliminate the need for coupling capacitors that are too large to be placed on an IC chip.

- ✓ The level shifter stage may be one or more level shifters that are included to ensure that there is no dc offset in the output signal.

- ✓ In addition, these intermediate stages may be used to convert the signal from differential (doubleended) mode to single-ended mode.

#### 3. Output stage:

- ✓ The output stage, or **power output stage**, also serves a dual purpose.

- $\checkmark$  It must supply the current required by the load without dissipating too much power in the output transistors.

- ✓ The output stage should provide a low output impedance to allow coupling to a low impedance load without loss of gain.

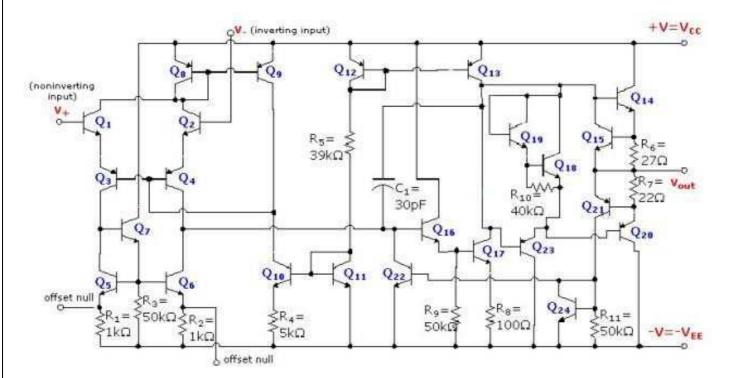

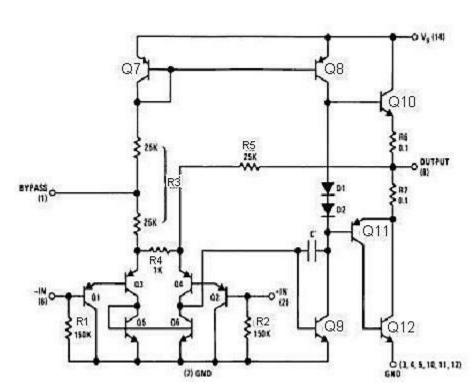

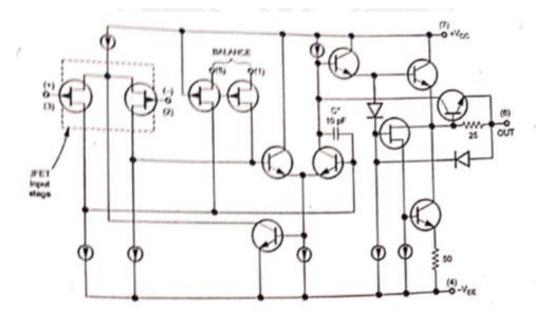

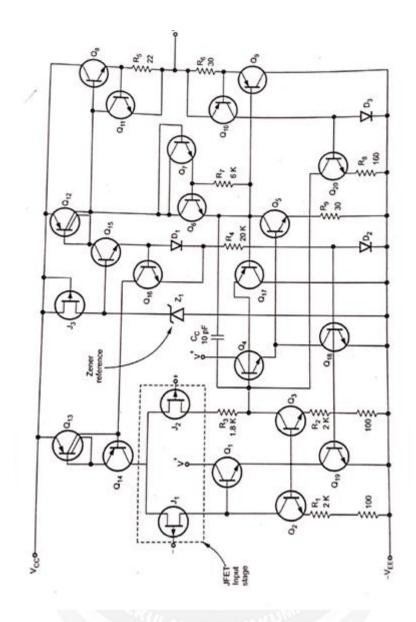

#### **1.9. INTERNAL CIRCUIT DIAGRAMS OF IC 741**

#### **1.10.AC CHARACTERISTICS OF AN OP-AMP**

- 1. Frequency Response

- 2. Circuit Stability

- 3. Slew Rate

- 4. Frequency Compensation

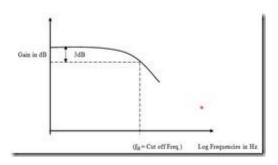

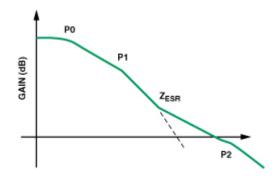

#### **<u>1. Frequency Response:</u>**

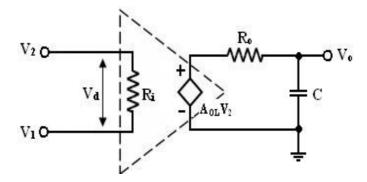

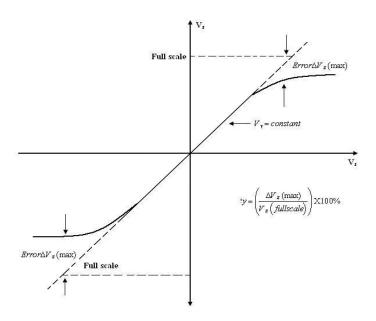

$\checkmark$  The variation in operating frequency will cause variations in gain magnitude and its phase angle.

$\checkmark$  The gain of the op-amp responds to different frequencies is called the frequency response.

- ✓ Op-amp should have an infinite bandwidth BW =∞.

- ✓ If its open loop gain in 90dB with dc signal, its gain should remain the same 90 dB through audio and onto high radio frequency.

- $\checkmark$  The op-amp gain decreases (roll-off) at higher frequency.

- ✓ There is a capacitive component in the equivalent circuit of the op-amp, decrease gain after a certain frequency reached.

- ✓ For an op-amp with only one break (corner) frequency, all the capacitors effects can be represented by a single capacitor C.

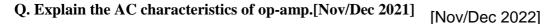

- $\checkmark$  Variation of the low frequency model with capacitor C at the output is shown in fig.

Equivalent circuit of practical circuit

- ✓ There is one pole due to  $R_0C$  and one -20dB/decade.

- $\checkmark$  The open loop voltage gain of an op-amp with only one corner frequency is obtained from above fig.

- $\checkmark$  f<sub>1</sub> is the corner frequency or the upper 3 dB frequency of the op-amp.

# ✓ The magnitude and phase angle characteristics:

- 1. For frequency f $\ll$  f1, the magnitude of the gain is 20 log AOL in db.

- 2. At frequency f = f1, the gain in 3 dB down from the dc value of AOL in db.

This frequency f1 is called corner frequency.

3. For f >> f1, the fain roll-off at the rate off -20dB/decade or -6dB/decade.

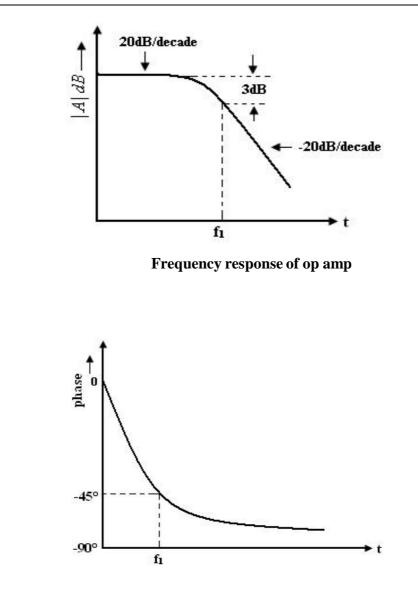

## 2. Circuit Stability:

## Q. Explain various stability criteria of op-amp. [Nov 2006]

- ✓ A circuit or a group of circuit connected together as a system is said to be stable, if its output reaches a fixed value in a finite time.

- $\checkmark$  A system is said to be unstable, if its output increases with time instead of achieving a fixed value.

- $\checkmark$  Bode plots are compared of magnitude Vs Frequency and phase angle Vs frequency.

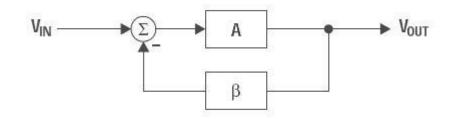

- $\checkmark$  Any system whose stability is to be determined can represented by the block diagram.

#### Feedback loop system

- $\checkmark$  The block between the output and input is referred to as forward block.

- $\checkmark$  The block between the output signal and feedback signal is referred to as feedback block.

- $\checkmark$  The content of each block is referred as transfer frequency.

AOL (f) = V0 /Vin if Vf = 0 ----- (1)

where AOL (f) = open loop volt gain.

- ✓ The closed loop gain Af is given by AF = VO / Vin = AOL / (1 + (AOL) (B) ----(2))

- ✓  $\mathbf{B}$  = gain of feedback circuit.

- $\checkmark$  B is a constant if the feedback circuit uses only resistive components.

- ✓ Once the magnitude Vs frequency and phase angle Vs frequency plots are drawn, system stability may be determined as follows

#### Method 1:

- $\checkmark$  Determine the phase angle when the magnitude of (AOL) (B) is 0dB (or) 1.

- ✓ If phase angle is >-180, the system is stable.

- $\checkmark$  However, some systems the magnitude may never be 0, in that cases method 2, must be used.

#### Method 2:

- $\checkmark$  Determine the phase angle when the magnitude of (AOL) (B) is 0dB (or) 1.

- $\checkmark$  If phase angle is > 180, the magnitude is -ve decibels then the system is stable.

- ✓ However, some systems the phase angle of a system may reach -1800, under such conditions method 1 must be used to determine the system stability.

#### **3.Slew Rate:**

#### Q. Define slew rate and describe the methods to improve slew rate. [Nov 2005, 08, 2009, May 2009,

Dec 2018]

- $\checkmark$  The slew rate is defined as the maximum rate of change of output voltage caused by a step input voltage.

- $\checkmark$  An ideal slew rate is infinite.

- ✓ Slew rate is the maximum rate of change of output voltage with respect to time.

- ✓ It is specified in V/ $\mu$ s.

#### **Reason for Slew rate:**

$\checkmark$  The rate at which the volt across the capacitor increases is given by

dVc/dt = I/C -----(1)

- ✓ I -> Maximum amount furnished by the op-amp to capacitor C.

- $\checkmark$  Op-amp should have the either a higher current or small compensating capacitors.

# 4. Frequency Compensation:

- ✓ Frequency compensation is needed when large bandwidth and lower closed loop gain is desired.

- $\checkmark$  Compensating networks are used to control the phase shift and hence to improve the stability.

# Frequency compensation methods:

- 1. External compensation

- a. Dominant- pole compensation

- b. Pole- zero compensation

- 2. Internal compensation

# **1.11.DC CHARACTERISTICS OF AN OP-AMP**

# Q. Explain the DC characteristics of op-amp.

DC characteristics of op amp are,

- 1. Input bias current

- 2. Input offset current

- 3. Input offset voltage

- 4. Thermal drift

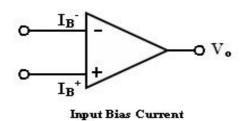

# 1. Input bias current:

Input bias current  $I_{B is}$  defined as the average value of the base currents entering into terminal of an opamp.

$$I_{B} = (I_{B}^{+} + I_{B}^{-}) / 2$$

#### 2.Input offset current

The difference between the bias currents at the input terminals of the op- amp is called as input offset current.

$IOS = IB^+ - IB^-$

The input terminals conduct a small value of dc current to bias the input transistors. Since the input transistors cannot be made identical, there exists a difference in bias currents

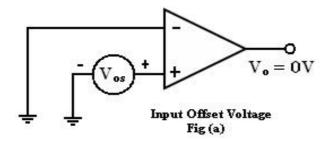

# 3. Input offset voltage

A small voltage applied to the input terminals to make the output voltage as zero when the two input terminals are grounded is called **input offset voltage**

#### 4. Thermal drift

Bias current, offset current and offset voltage change with temperature.

A circuit carefully nulled at  $25^{\circ}$ c may not remain so when the temperature rises to  $35^{\circ}$ c. This is called **drift**.

#### **1.12. OPEN LOOP OP-AMP CONFIGURATION**

#### Q. Explain the open loop configuration of op-amp with example circuits. (Nov 2016)

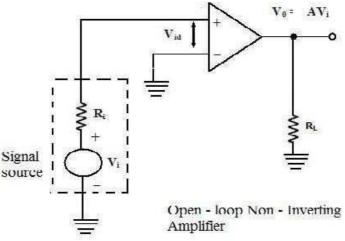

- $\checkmark$  The term open-loop indicates that no feedback in any form is fed to the input from the output.

- $\checkmark$  When connected in open loop, the op-amp functions as a very high gain amplifier.

- $\checkmark$  There are three open loop configurations of op-amp namely,

- 1. Differential amplifier

- 2. Inverting amplifier

- 3. Non-inverting amplifier

- ✓ The above classification is made based on the number of inputs used and the terminal to which the input is applied.

- $\checkmark$  The op-amp amplifies both ac and dc input signals.

- $\checkmark$  Thus, the input signals can be either ac or dc voltage.

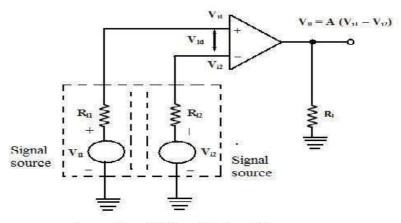

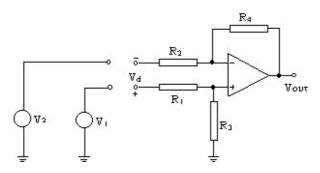

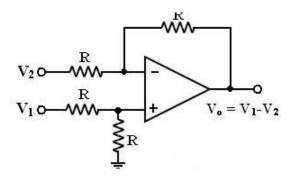

#### 1. Differential Amplifier:

- ✓ In this configuration, the inputs are applied to both the inverting and the noninverting input terminals of the op-amp.

- $\checkmark$  It amplifies the difference between the two input voltages.

Open - loop Differential Amplifier

- ✓ Figure shows the open-loop differential amplifier configuration.

- $\checkmark$  The input voltages are represented by Vi1 and Vi2.

- ✓ The source resistance Ri1and Ri2 are negligibly small in comparison with the very high input resistance offered by the op-amp.

- $\checkmark$  Thus the voltage drop across these source resistances is assumed to be zero.

- $\checkmark$  The output voltage V<sub>0</sub> is given by

$$V_0 = A (V_{i1} - V_{i2})$$

where A is the large signal voltage gain.

- $\checkmark$  Thus the output voltage is equal to the voltage gain A times the difference between the two input voltages.

- $\checkmark$  This is the reason why this configuration is called a differential amplifier.

- $\checkmark$  In open loop configurations, the large signal voltage gain A is also called open-loop gain A.

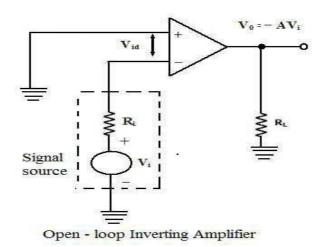

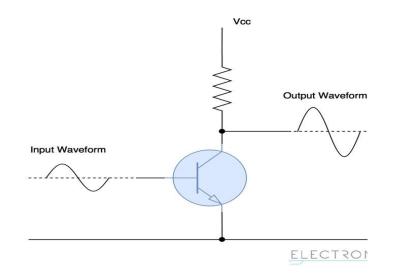

## 2. Inverting amplifier:

- ✓ In this configuration, the input signal is applied to the inverting input terminal of the op amp and the non-inverting input terminal is connected to the ground.

- $\checkmark$  Figure shows the circuit of an open loop inverting amplifier.

- $\checkmark$  The output voltage is 180 out of phase with respect to the input.

- $\checkmark$  Hence, the output voltage V0 is given by,

$$V0 = -AVi.$$

✓ Thus, in an inverting amplifier, the input signal is amplified by the open-loop gain A and in phase shifted by  $180^{\circ}$ .

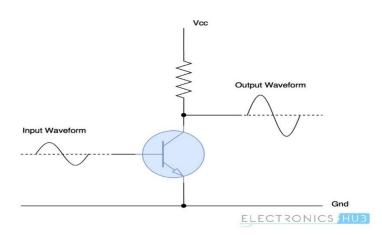

# **<u>3.Non-inverting Amplifier:</u>**

- ✓ Figure shows the open loop non- inverting amplifier.

- ✓ The input signal is applied to the non-inverting input terminal of the op-amp and the inverting input terminal is connected to the ground.

- $\checkmark$  The input signal is amplified by the open loop gain A and the output is in-phase with input signal.

$$V_0 = AVi$$

# Limitations of Open – loop Op – amp configuration:

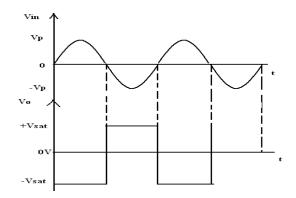

- ✓ In the open loop configurations, clipping of the output waveform can occur when the output voltage exceeds the saturation level of op-amp.

- ✓ This is due to the very high open loop gain of the op-amp.

- ✓ The open loop gain of the op amp is not a constant.

- $\checkmark$  It varies with changing temperature and variations in power supply.

- $\checkmark$  Also, the bandwidth of most of the open- loop op amps is negligibly small.

- $\checkmark$  This makes the open loop configuration of op-amp unsuitable for ac applications.

# **1.13. CLOSED LOOP OP-AMP CONFIGURATION**

## Q. Explain the inverting and Non-inverting amplifier of closed loop configurations. [Dec 2018]

- ✓ The op-amp can be effectively utilized in linear applications by providing a feedback from the output to the input, either directly or through another network.

- ✓ If the feedback signal is out of- phase by 1800 with respect to the input, then the feedback is referred to as negative feedback or degenerative feedback.

- ✓ If the feedback signal is in phase with respect to the input, then the feedback is referred to as positive feedback or regenerative feedback.

- $\checkmark$  An op amp that uses feedback is called a closed loop amplifier.

- $\checkmark$  The most commonly used closed loop amplifier configurations are

- 1. Inverting amplifier (Voltage shunt amplifier)

- 2. Non- Inverting amplifier (Voltage series Amplifier)

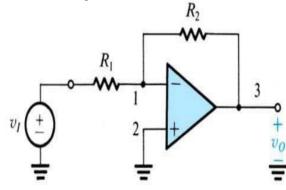

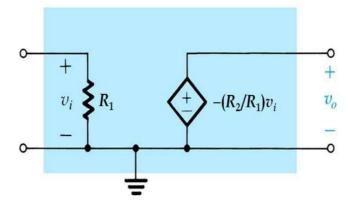

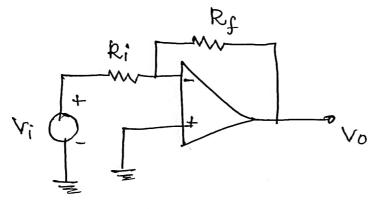

#### The inverting close-loop configuration

- ✓ External components R1 and R2 form a close loop

- $\checkmark$  Output is fed back to the inverting input terminal

- ✓ Input signal is applied from the inverting terminal

- $\checkmark$  The required conditions to apply virtual short for op-amp circuit:

- Negative feedback configuration

- Infinite open- loop gain

- ✓ Closed loop gain:  $G \equiv VO / VI = -R2 / R1$

- ✓ Infinite differential gain: V2 V1 = V0 /A = 0

- ✓ Infinite input impedance: i2 = i1 = 0

- ✓ Zero output impedance: VO = V1 i1R2 = -vIR2/R1

- ✓ Voltage gain is negative: Input and output signals are out of phase

- ✓ Closed loop gain depends entirely on external passive components (independent of op-amp gain)

- ✓ Close loop amplifier trades gain (high open loop gain) for accuracy (finite but accurate closed loop gain)

Equivalent circuit model for the inverting configuration

- ✓ Input impedance:  $Ri \equiv vI / iI = vI / (vI / R1) = R1$

- ✓ For high input closed loop impedance, R1 should be large, but is limited to provide sufficient G

- $\checkmark$  In general, the inverting configuration suffers from a low input impedance

- $\checkmark$  Output impedance: Ro = 0

- ✓ Voltage gain: Avo = R2/R1

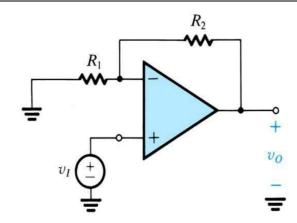

#### 2.<u>Non inverting closed loop Configuration:</u>

- ✓ External components R1 and R2 form a close loop

- ✓ Output is fed back to the inverting input terminal Input signal is applied from the noninverting terminal.

- $\checkmark$  The required conditions to apply virtual short for op- amp circuit:

- Negative feedback configuration

- Infinite open loop gain

- ✓ Closed loop gain:  $G \equiv VO / VI = 1 + R2 / R1$

- ✓ Infinite differential gain:  $V_+ V_- = V_0 / A = 0$

- ✓ Infinite input impedance: i2 = i1 = V /R1

- ✓ Zero output impedance:  $V_0 = V_{-} + i_1R_2 = V_I (1 + R_2 / R_1)$

- ✓ Closed loop gain depends entirely on external passive components (independent of op amp gain)

✓ Close loop amplifier trades gain (high open loop gain) for accuracy (finite but accurate closed loop gain)

Equivalent circuit model for the noninverting configuration

- ✓ Input impedance: Ri = Infinite

- ✓ Output impedance: Ro = 0

#### TWO MARKS

#### 1. Define an integrated circuit. (or) what is an integrated circuit? [May 2010]

An integrated circuit (IC) is a miniature, low cost electronic circuit consisting of active and passive components fabricated together on a single crystal of silicon. The active components are transistors and diodes and passive components are resistors and capacitors.

#### 2. Mention the advantages of integrated circuits.

The advantages of integrated circuits are,

- ✓ Miniaturization and hence increased equipment density.

- $\checkmark$  Cost reduction due to batch processing.

- $\checkmark$  Increased system reliability due to the elimination of soldered joints.

- $\checkmark$  Improved functional performance.

- ✓ Matched devices.

- ✓ Increased operating speeds. Reduction in power consumption

# 3. Define Current mirror circuit & List out its advantages. (or) What is current mirror? [April/May 2010, Nov/Dec 2011]

A circuit in which the output current is equal to input current is called current mirror

circuit. In current mirror circuit, the output current is the mirror image of the input current.

#### Advantages:

- a. High CMRR

- b. Easy to design

- 4. Draw the current mirror circuit.

$$I_{REF} \downarrow I_{E} \downarrow I_$$

#### 5. Give the basic concept of current source.

A constant current source makes use of the fact that for a transistor in the active mode of operation, the collector current is relatively independent of collector voltage.

#### 6. What are the applications of current sources?

The applications of current sources are:

- i. The emitter resistance in differential amplifier to increase CMRR.

- ii. As an active load to provide high a.c.resistance without disturbing the d.c conditions.

#### 7. Give the limitation of current mirror circuit.

The limitation of current mirror circuit is whenever we need low value of current, the value of resistance is high and it cannot be fabricated economically in IC circuits

#### 8. Justify the reasons for using current sources in integrated circuits.

- 1. Superior insensitivity of circuit performance to power supply variations and temperature.

- 2. More economical than resistors in terms of die area required providing bias currents of small value.

- 3. When used as load element, the high incremental resistance of current source results in high voltage gains at low supply voltages.

#### 9. What is the advantage of widlar current source over constant current source?

Using constant current source, the output current of small magnitude (microamp range) is not attainable due to the limitations in chip area. Widlar current source is useful for obtaining small output currents. Sensitivity of widlar current source is less compared to constant current source.

#### 10. Mention the advantages of Wilson current source.

The advantages of Wilson current sources are:

- ✓ Provides high output resistance.

- ✓ Offers low sensitivity to transistor base currents.

#### 11. What is voltage source?

A voltage source is a circuit that produces an output voltage (V<sub>0</sub>), which is independent of the load driven by the voltage source or the output current supplied to the load.

#### 12. Give advantages of emitter follower voltage source.

The advantages of emitter follower are:

- a. It produces low ac impedance

- b. Gives effective decoupling of adjacent gain stages.

## 13. Write the limitation of emitter follower or common collector voltage source.

Emitter follower voltage source is weak and without protection for changes in bias voltage and the output voltage with respect to changes in supply voltage.

## 14. What is voltage reference? [Nov/Dec 2021]

The circuit that is designed for providing a constant voltage independent of changes in temperature is called a voltage references.

## 15. Define temperature coefficient.

Temperature coefficient is the measure of the ability of the circuit to maintain the standard output voltage under varying temperature conditions.

$$TC(V_0) = dV_0/dT \text{ in } mV/^0 C$$

## 16. What are the properties of voltage reference?

The Properties of voltage reference are:

- i. Reference voltage must be independent any temperature change.

- ii. It must have good power supply rejection which is independent of the supply voltage.

- iii. The circuit should have low output impedance.

#### 17. What are the parameters of voltage reference circuits?

The Parameters of voltage reference are:

- i. Line regulation

- ii. Load regulation

- iii. Long term stability

- iv. Ripple rejection ratio.

# **18. Define line regulation.**

Line regulation is defined as the ratio of change in output voltage to the change in input voltage.

Line regulation =  $\Delta V_0 / \Delta V_i$

Where  $\Delta V_{O}-changes$  in the output line voltage

$\Delta V_i$  - changes in the input line voltage It is expressed in mV/V

# **19. Define load regulation.**

Load regulation is defined as the ratio of change in output voltage to the change in load current. Load regulation =  $\Delta V_0 / \Delta I_L$

Where  $\Delta V_0$  – changes in the output line voltage

$\Delta IL$  - changes in the load current It is expressed in mV/mA

## 20. What is long term stability?

The ability of the circuit to maintain the output voltage constant with respect to time is given by the parameter long term stability. It is measured in ppm/1000 hours.

## 21. Define Ripple Rejection Ratio (RRR).

The ability of the circuit to reject input ripples and an indication of how much ripples are present at the output due to input is given by the factor RRR. It is defined as  $RRR = 20 \log_{10}[V_{ri}/V_{ro}]$  Where  $V_{ri}$  - Input ripple and  $V_{ro}$  –Output ripple

# 22. What are the limitations in a temperature compensated zener-reference source?

#### Limitations of zero reference source:

A power supply voltage of at least 7 to 10 V is required to place the diode in the breakdown region and that substantial noise is introduced in the circuit by the avalanching diode.

# 23. What is differential amplifier? Need for differential amplifier. [Nov/Dec 2022]

A circuit which amplifies the difference between two input voltage signals. Hence it is also called as difference amplifier.

# 24. Draw the block diagram for differential amplifier.

#### 25. What are the properties of differential amplifier?

The Properties of differential amplifier are:

- i. Excellent stability

- ii. High versatility

- iii. High immunity to interference signals.

#### 26. Give the advantages of differential amplifier.

The advantages of differential amplifier are:

- 1. Lower cost

- 2. IC fabrication is easy

- 3. Closely matched components

## 27. Define differential gain.

Differential gain is defined as the ratio of the output voltage to the difference voltage.

$$A_d = V_0 / V_d ,$$

In decibel 20 log10  $A_d = 20 \log_{10} V_0 / V_d$

# 28. Why are active loads preferred than passive loads in the input stage of an operational amplifier? [Nov/Dec 2010] [Nov/Dec 2022]

Differential amplifier designed with active load to increase the CMRR. The gain increased

by using large value of collector resistances. If the collector resistance is large then limitation in IC

fabrications are large chip area and large bias voltage need.

# 29. Define CMRR. [May/June 2004, Nov/Dec 2005, Nov/Dec 2009, Nov/Dec 2010]

The common Mode Rejection ratio (CMRR) is defined as the ration of difference modegain to the common mode gain

CMRR = |ADM/ACM|

It is expressed in decibel (dB)

# 30. What are the draw backs of using large RC in differential amplifier?

The main draw backs are: It requires large chip area. For larger RC quiescent drop, a large power supply will be required to maintain a given quiescent collector current.

#### 31. What is active load? Where it is used and why?

The requirement to increase the gain is same that the collector resistance (RC) should not disturb d.c conditions while it must provide large resistance for a.c purposes. The current mirror which has very low d.c resistance (dV/dI) and higher a.c resistance (dv/di) can be used as a collector load instead of RC. Such a load is called as active load.

## 32. What is an operational amplifier? [Nov/Dec 2005]

An operational amplifier is a direct-coupled, high gain amplifier consisting of one or more differential amplifier. By properly selecting the external components, it can be used to perform a variety of mathematical operations.

#### 33. What are the popular IC packages available?

The IC packages available are:

- ✤ Metal can package.

- ✤ Dual-in-line package.

- ✤ Ceramic flat package.

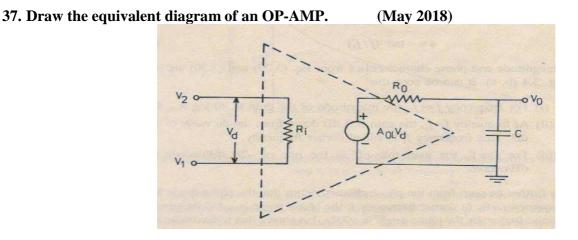

- 34. List out the ideal characteristics, and draw the equivalent diagram of an OP-AMP Mention any four important characteristics of ideal operational amplifier. [May/June2003, May/June2009, Nov/Dec2010]

The Ideal characteristics of op-amp are:

- ✤ Open loop voltage gain is infinity.

- ✤ Input impedance is infinity.

- Output impedance is zero.

- Bandwidth is infinity.

- Zero offset

- Infinite CMRR

- Infinite slew rate

- PSRR = 0

## 36. Define Virtual ground property of an OP-AMP.

A virtual ground is a ground which acts like a ground. It may not have physical connection to ground. This property of an ideal op-amp indicates that the inverting and non-inverting terminals of op-amp are at the same potentials. The non-inverting input is grounded for the inverting amplifier circuit. This means that the inverting input of the op-amp is also at ground potential.

#### 38. What are the stages in op-amp?

The stages of op-amp are:

- a. Input stage

- b. Gain stage

- c. Output stage

## 39. What are the requirements of the input stage of an op-amp?[May/June 2010]

The differential amplifier eliminates the need for an emitter bye-pass capacitor. So, differential amplifier is used as an input stage in op-amp ICs

#### 40. In what way 741S is better than 741? [Nov/Dec2003]

741S is a military grade op-amp with higher slew rate

#### 41. Why is IC741 op-amp not used for high frequency applications?

Op-amp IC741 has very low slew rate and therefore cannot be used for high frequency applications

#### 42. Define Input bias current. [May/June 2009]

Input bias current IB is the average of the currents that flow into the inverting and non-inverting input terminals of the op-amp.

i.e. IB = (IB1 + IB2)/2

#### 43. Define Input offset current. [May/June 2009]

The algebraic difference between the current into the inverting and non-inverting terminals is referred to as input offset current Iio. Mathematically it is represented as Iios= |IB+ - IB- |

Where I B+ is the current into the non-inverting input terminals.

IB- is the current into the inverting input terminals.

#### 44. What is Input offset voltage?

Input offset voltage is the voltage required to be amplified at the input for making output voltage to zero volts.

# 45. Determine the slew rate of the op-amp. Or Define slew rate. (May/June2003, Nov/Dec2010, Nov/Dec2011, May/June 2008]

Slew rate can be defined as the maximum rate of change of output voltage of op-amp with respect to time. It is expressed as S = (dVo / dt) max in V/Sec.Where slew rate  $S = 2\Pi f Vm$  in V/Sec.

#### 46. What is a compensating network?

The networks formed by components such as resistors and capacitors for modifying the rate of change of gain and the phase shift is called as compensating network

#### 47. When are the internally compensating systems used?

In applications where the op-0amp is required to amplify relatively slow changing signals and does not require good high frequency response, internally compensating systems are used.

# 48. In response to a square wave input, the output of an op-amp changed from -3V to +3V over a time interval of 0.25μs, find slew rate. (May '06)

Slew rate=  $\Delta Vo/\Delta t = 6/0.25=24 V/\mu s$ .

# **49.** List the types of frequency compensation.

- a. External frequency compensation

- 1. Dominant pole freq. compensation

- 2. Pole zero freq. compensation

- b. Internal frequency compensation.

#### 50. List the DC characteristics of op amp.

DC characteristics of op-amp are:

- 1. Input bias current

- 2. Input offset current

- 3. Input offset voltage

- 4. Thermal drift.

# 51. List the AC characteristics of opamp. (Dec 2018)

AC characteristics of op-amp are:

- 1. Frequency response

- 2. Stability of an op-amp,

- 3. Frequency compensation

- 4. Slew rate.

## 52. What is the need for frequency compensation in practical op-amps?

Frequency compensation is needed when large bandwidth and lower closed loop gain is desired. Compensating networks are used to control the phase shift and hence to improve the stability.

## 53. What are the merits of Dominant-pole compensation?

The merits of Dominant-pole compensation are:

- 1.Noise immunity of the system is improved.

- 2. Open-loop bandwidth is reduced.

# 54. What is the maximum undistorted amplitude, that a sine wave input of 10 KHz, can produce, at the output of an op-amp whose slew rate is 0.5V/µs? (Nov '12)

Given F=10KHZ and slew rate (S) =  $0.5V/\mu s$

Solution: Slew rate (S) =  $2\pi f V m V / \mu s$ .

Maximum amplitude (Vm) =  $S/2\pi f$  =7.92V

# 55. The op-amp has a gain of 12 million. Express the gain in dB.(Nov '03)

Gain in dB=20log(gain)

$20 \log(20*10^6) = 141.6$ dB

# 56. What is the need for frequency compensation in practical op-amps?

Frequency compensation is needed when large bandwidth and lower closed loop gain is desired. Compensating networks are used to control the phase shift and hence to improve the stability.

# 57. Why open loop op-amp configurations are not used in linear applications?

- a. The open loop gain of the op-amp is very high. Therefore, only the smaller signals having low frequency may be amplified accurately without distortion.

- b. Open loop Voltage gain of the op-amp is not a constant voltage gain varies with changes in temperature and power supply as well as mass production techniques. This makes op-amp unsuitable for many linear applications

- c. Bandwidth of most open loop op-amps is negligibly small or almost zero therefore op-amp is impractical in ac applications.

# 58. In practical op-amps, what is the effect of high frequency on its performance?

The open-loop gain of op-amp decreases at higher frequencies due to the presence of parasitic capacitance. The closed-loop gain increases at higher frequencies and leads to instability.

# 59. What are the advantages of negative feedback?

Advantages of negative feedback are:

- 1. It reduces the gain and makes it controllable

- 2. It reduces the possibility of distortion

- 3. It increases the bandwidth

- 4. It increases the input resistance of the op-amp

- 5. It decreases the output resistance of the op-amp

- 6. It reduces the effect of temperature, power supply on the gain of the circuit.

## 60. Define Differential Mode gain.

## (Dec 2018)

Gain of an amplifier is defined as  $V_{OUT}/V_{IN}$ . For the special case of a differential amplifier, the input  $V_{IN}$  is the difference between its two input terminals, which is equal to  $(V_1-V_2)$  as shown in the following diagram.

# 61. What are the two methods can be used to produce voltage sources? (May 2018)

There are two methods used to produce a voltage source, namely,

- 1. Using the impedance transforming properties of the transistor,

- 2. Using an amplifier with negative feedback.

## 62. Why is slew rate is infinite in an ideal op-amp? [N0v/Dec 2021]

For an ideal operational amplifier, time delay is negligible. Hence it has an infinite slew rate. That means it can provide output voltage simultaneously with the input voltage changes.

#### UNIT-I

PARTB

D A THI Op-amp is used as an investing amplifier With a closed toop gain of 50. Find the maximum comput signal that can be applied to get undistosted output if frequency response is constant upto 20KHZ. [NUV ] Dec 202]

TXF

$$A_{\rm CL} = -\frac{R_{\rm f}}{R_{\rm f}} = 50$$

$$50R_1 = -R_f$$

$$\frac{V_0}{Vin} = 50$$

$$Vin = \frac{30}{50}$$

$$V_0 = V_{m} = \frac{S \times 10^6}{2 \pi x}$$

$$= \frac{2 \times 10^{10}}{2\pi \times 20 \times 10^{3}} = \frac{100}{2\pi}$$

$V_0 = 100$  $V_0 = 15.92 V.$   $V_{in} = \frac{15.92}{50}$ = 15.92V Vin = 30×10-2 . V.

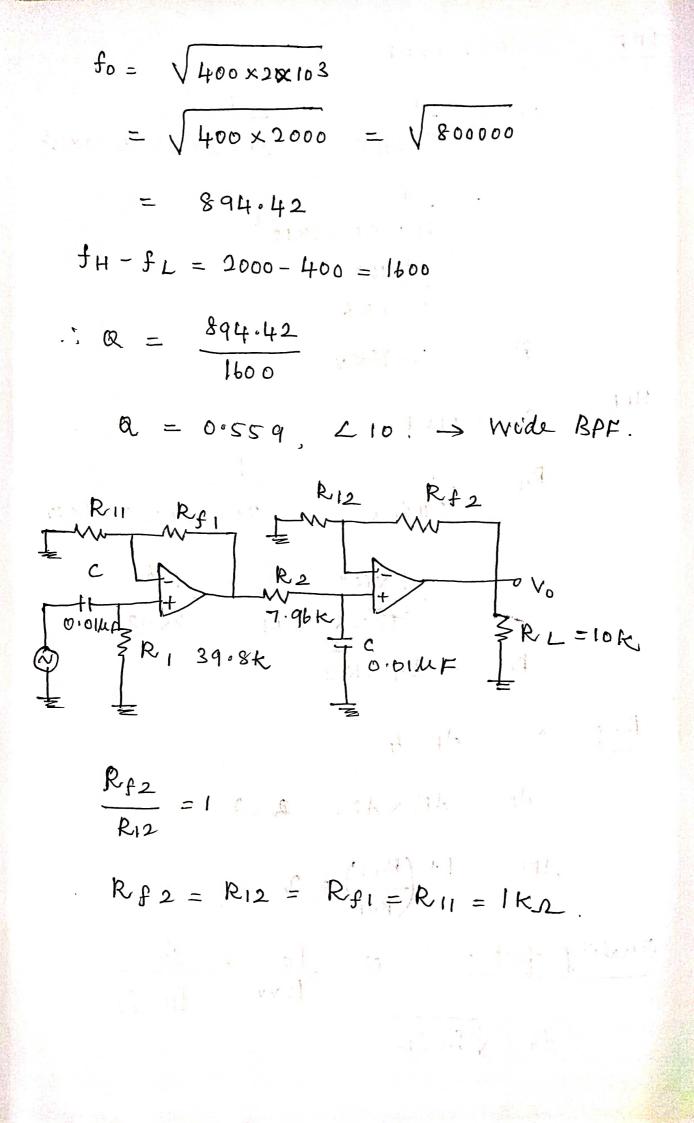

# <u>UNIT II</u>

# **APPLICATIONS OF OPERATIONAL AMPLIFIERS**

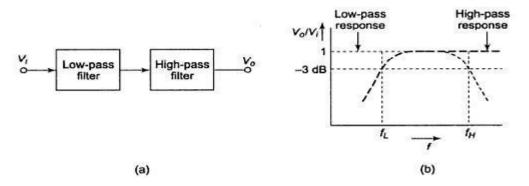

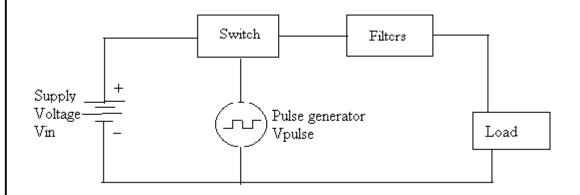

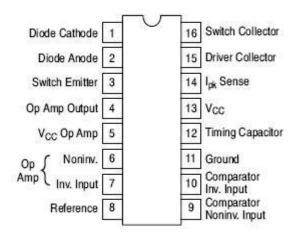

Sign Changer, Scale Changer, Phase Shift Circuits, Voltage Follower, V-to-I and I-to-V converters, adder, subtractor, Instrumentation amplifier, Integrator, Differentiator, Logarithmic amplifier, Antilogarithmic amplifier, Comparators, Schmitt trigger, Precision rectifier, peak detector, clipper and clamper, Low-pass, high-pass and band-pass Butterworth filters.

Sign Changer (Phase Inverter)

Explain sign changer and scale changer using op-amp.

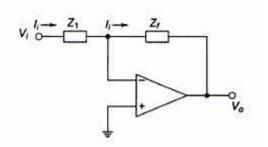

- The basic inverting amplifier configuration using an op-amp with input impedance Z1 and feedback impedance Zf.

- ✓ If the impedance Z1 and Z f are equal in magnitude and phase, then the closed loop voltage gain is -1, and the input signal will undergo a 180° phase shift at the output.

- $\checkmark$  Hence, such circuit is also called phase inverter.

- ✓ If two such amplifiers are connected in cascade, then the output from the second stage is the same as the input signal without any change of sign.

- ✓ Hence, the outputs from the two stages are equal in magnitude but opposite in phase and such a system is an excellent paraphase amplifier.

## Scale Changer:

- ✓ Referring the above diagram, if the ratio  $Z_f / Z_1 = k$ , a real constant, then the closed loop gain is k, and the input voltage is multiplied by a factor –k and the scaled output is available at the output.

- ✓ Usually, in such applications, Z<sub>f</sub> and Z<sub>1</sub> are selected as precision resistors for obtaining precise and scaled value of input voltage.

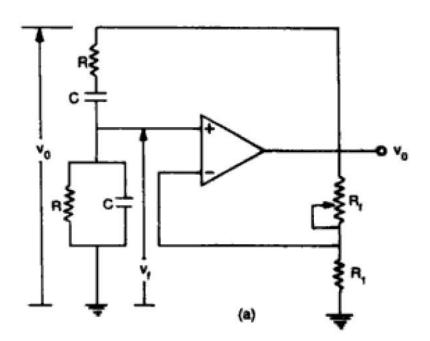

# **Phase Shift Circuits**

# Explain the phase shift circuits using op-amp.

- ✓ The phase shift circuits produce phase shifts that depend on the frequency and maintain a constant gain.

- $\checkmark$  These circuits are also called constant-delay filters or all-pass filters.

- ✓ That constant delay refers to time difference between input and output remains constant when frequency is changed over a range of operating frequencies.

- ✓ This is called all-pass because normally a constant gain is maintained for all the frequencies within the operating range.

$\checkmark$  The two types of circuits, for lagging phase angles and leading phase angles.

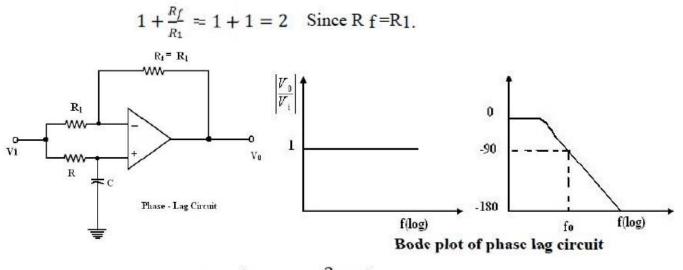

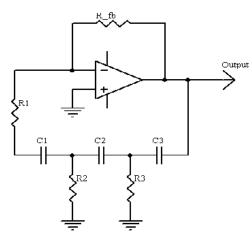

# **Phase-lag circuit:**

- ✓ Phase lag circuit is constructed using an op-amp, connected in both inverting and non-inverting modes.

- ✓ To analyze the circuit operation, it is assumed that the input voltage v1 drives a simple inverting amplifier with inverting input applied at(-)terminal of op-amp and a non-inverting amplifier with a low-pass filter.

- $\checkmark$  It is also assumed that inverting gain is -1 and non-inverting gain after the low-pass circuit is

$$V_o(jw) = -V_i(jw)\left(-1 + \frac{2}{1 + jwRC}\right)$$

and the relationship between output and input can be expressed by

$$\frac{V_0(jw)}{V_i(jw)} = \frac{(1-jwRC)}{(1+jwRC)}$$

The relationship is complex as defined above equation and it shows that it has both magnitude and phase. Since the numerator and denominator are complex conjugates, their magnitudes are identical and the overall phase angle equals the angle of numerator less the angle of the denominator.

$$\theta = -2 \tan^{-1} RC\omega$$

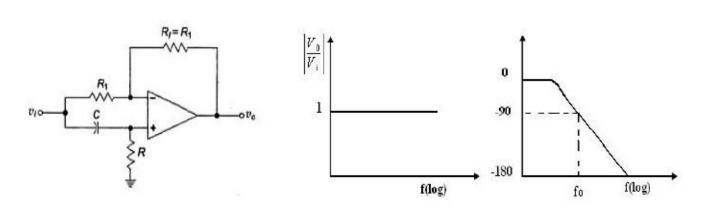

**Phases-lead circuit**

$$\frac{V_o(jw)}{V_i(jw)} = -\frac{(1-jwRC)}{(1+jwRC)}$$

$$\theta = 180^\circ - 2 \tan^{-1} RC\omega$$

## Phase lead circuit

Bode plot of Phase lead circuit

- ✓ Phase lead circuit is constructed using an op-amp, connected in both inverting and non-inverting modes.

- ✓ To analyze the circuit operation, it is assumed that the input voltage v1 drives a simple inverting amplifier with inverting input applied at(-)terminal of op-amp and a non-inverting amplifier with a High-pass filter.

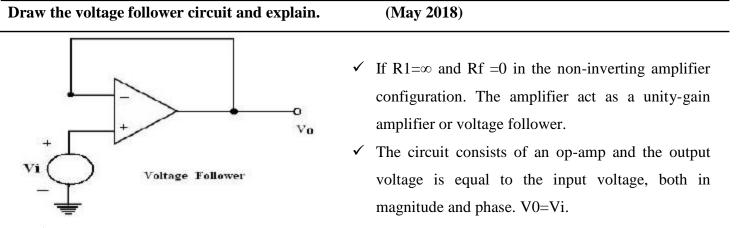

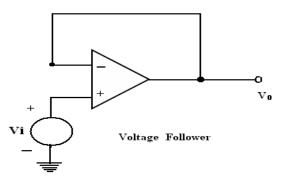

# Voltage follower:

- ✓ Since the output voltage of the circuit follows the input voltage, the circuit is called voltage follower.

- ✓ It offers very high input impedance of the order of MΩ and very low output impedance.

- ✓ Therefore, this circuit draws negligible current from the source.

- ✓ Thus, the voltage follower can be used as a buffer between a high impedance source and a low impedance load for impedance matching applications.

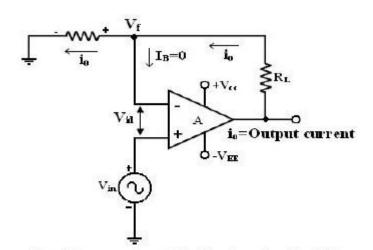

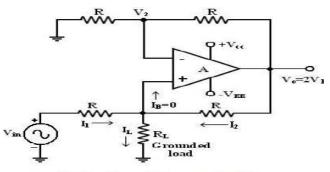

Voltage to Current Converter with floating loads (V/I) [Nov/Dec 2022]

Explain voltage to current converter using op-amp. (Nov 2006, 2016, May 2018) [Nov/Dec 2021]

✓ Voltage to current converter in which load resistor RL is floating (not connected to ground).

Vin is applied to the non- inverting input terminal, and the feedback voltage across R1 devices the inverting input terminal.

✓ This circuit is also called as a current – series negative feedback amplifier.

V to I Converter with floating loads (V/I)

✓ Because the feedback voltage across R1 (applied Non-inverting terminal) depends on the output current i0 and is in series with the input difference voltage Vid.

Writing KVL for the input loop,

Voltage  $V_{id} = V_f$  and  $I_B = 0$ ,  $V_i = R_L i_o$  where  $i_o = \frac{V_i}{R_L}$

- ✓ From the fig input voltage Vin is converted into output current of Vin/RL [Vin -> i0].

- ✓ In other words, input volt appears across R1. If RL is a precision resistor, the output current (i0 = Vin/R1) will be precisely fixed.

# **Applications:**

- 1. Low voltage ac and dc voltmeters

- 2. Diode match finders

- 3. LED and Zener diode testers.

# Voltage - to current converter with Grounded load

V – I converter with grounded load

EC8453 / Linear Integrated Circuits

✓ This is the other type V – I converter, in which one terminal of the load is connected to ground.

# Analysis of the circuit:

- $\checkmark$  The analysis of the circuit can be done by following 2 steps.

- 1. To determine the voltage V1 at the non-inverting (+) terminals and

- 2. To establish relationship between V1 and the load current IL. Applying KCL at node a,

$$R = Rf$$

$$I1 + I2 = IL$$

$$(Vi+Va)/R + (Vo - Va)/R = IL$$

$$Vo = (Vi + Vo - IL R)/2 \text{ and } gain = 1 + R/R = 2.$$

$$\therefore V_i = I_L R ; I_L = V_i/R$$

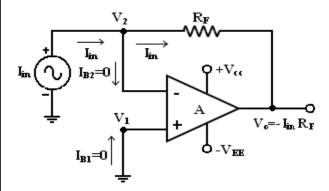

Current to Voltage Converter (I –V):

# Explain current to voltage converter using op-amp. (Nov 2016)[Nov/Dec2021]

Open – loop gain A of the op-amp is very large. Input impedance of the op amp is very high.

# Sensitivity of the I – V converter:

- 1. The output voltage V0 = -RF Iin.

- Hence the gain of this converter is equal to -RF. The magnitude of the gain (i.e.) is called as sensitivity of I to V converter.

- 3. The amount of change in output volt  $\Delta V0$  for a given change in the input current  $\Delta Iin$  is decide by the sensitivity of I-V converter.

- 4. By keeping RF variable, it is possible to vary the sensitivity as per the requirements.

# Applications of I – V Converter:

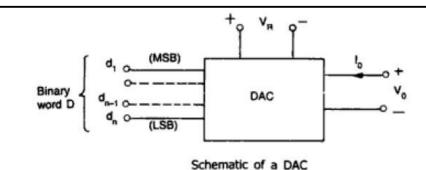

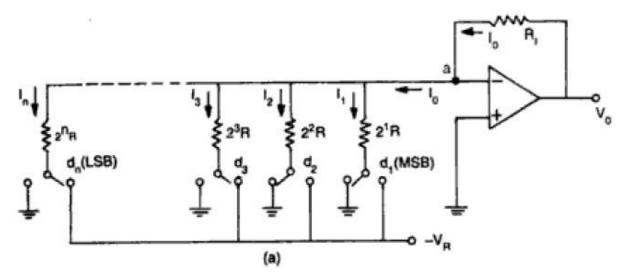

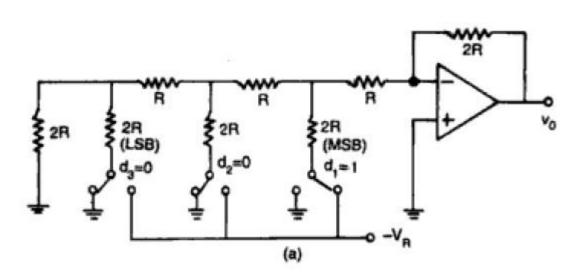

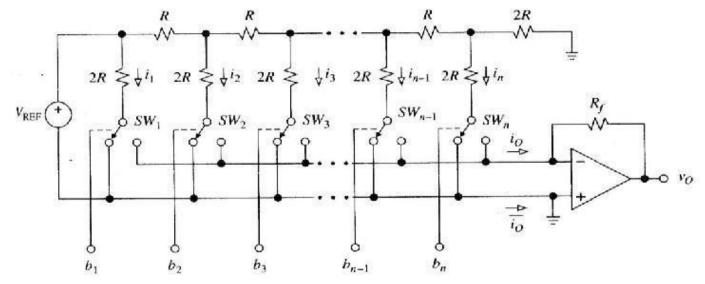

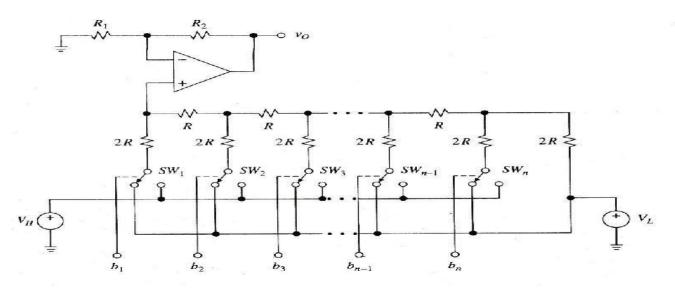

One of the most common uses of the current to voltage converter is

- 1. Digital to analog Converter (DAC)

- 2. Sensing current through Photo detector. Such as photo cell, photo diodes and photovoltaic cells.

Photoconductive devices produce a current that is proportional to an incident energy or light (i.e). It can be used to detect the light.

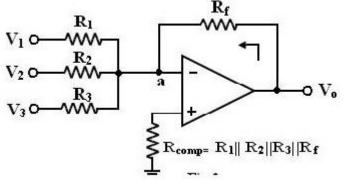

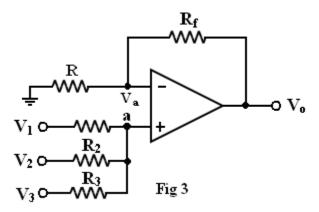

#### Adder:

✓ Op-amp may be used to design a circuit whose output is the sum of several input signals. Such a circuit is called a summing amplifier or a summer or adder.

## **Inverting Summing Amplifier:**

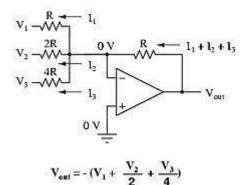

- ✓ A typical summing amplifier with three input voltages V1, V2 and V3 three input resistors R1, R2, R3 and a feedback resistor Rf is shown in figure.

- ✓ The op-amp is an ideal one, AOL= ∞.

- $\checkmark$  Since the input bias current is assumed to be

zero, there is no voltage drop across the resistor Rcomp and hence the non-inverting input terminal is at ground potential.

6

$$I = V1/R1 + V2/R2 \dots + Vn/Rn;$$

$Vo = -Rf I = Rf/R(V1 + V2 + \dots Vn).$

- ✓ To find Rcomp, make all inputs V1 = V2 = V3 = 0.

- ✓ So the effective input resistance  $Ri = R1 \parallel R2 \parallel R3$ .

- ✓ Therefore,  $\text{Rcomp} = \text{Ri} \parallel \text{Rf} = \text{R1} \parallel \text{R2} \parallel \text{R3} \parallel \text{R,f.}$

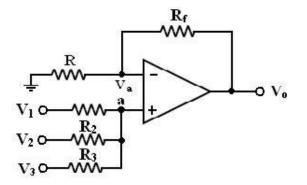

## Non-Inverting Summing Amplifier:

Subtractor: (Write short notes on subtractor.) (May 2018)

- ✓ A summer that gives a non-inverted sum is the noninverting summing amplifier of figure

- ✓ Let the voltage at the (-) input terminal be Va. which is a non-inverting weighted sum of inputs.

- ✓ Let R1 = R2 = R3 = R = Rf/2, then Vo = V1+V2+V3

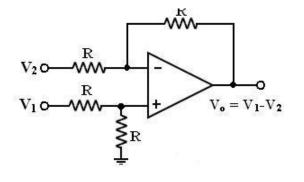

- ✓ A basic differential amplifier can be used as a subtractor as shown in the above figure.

- ✓ If all resistors are equal in value, then the output voltage can be derived by using superposition principle.

- ✓ To find the output V01 due to V1 alone, make V2 = 0.

- ✓ Then the circuit of figure as shown in the above becomes a non-inverting amplifier having input voltage V1/2 at the non-inverting input terminal and the output becomes

V01 = V1/2(1+R/R) = V1 when all resistances are R in the circuit.

- ✓ Similarly the output V02 due to V2 alone (with V1 grounded) can be written simply for an inverting amplifier as V02 = -V2

- ✓ Thus the output voltage Vo due to both the inputs can be written as V0 = V01 V02 = V1 V2

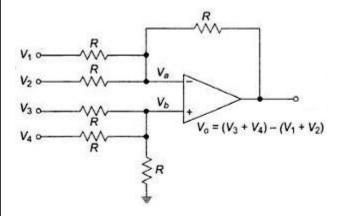

# Adder/Subtractor:

- ✓ It is possible to perform addition and subtraction simultaneously with a single op-amp using the circuit shown in figure

- ✓ The output voltage Vo can be obtained by using superposition theorem.

- ✓ To find output voltage V01 due to V1 alone, make all other input voltages V2, V3 and V4 equal to zero.

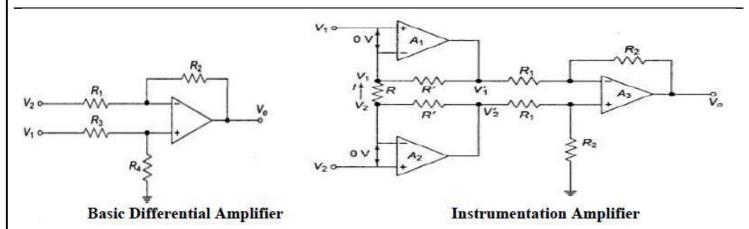

**Instrumentation Amplifier:**

Explain operation of instrumentation amplifier. Name two applications of the same. (Nov 2003, May 2005, 2008, Dec 2018)

✓ Current flowing in resistor R is I= (V1-V2)/R and it flow through R' in the direction shown, Voltage at non-inverting terminal op-amp A3 is R2V1<sup>'</sup>/(R1+R2).

✓ By superposition theorem,

Vo= (R2/R1)V1+(1+R2/R1)(R2V2/(R1+R2)=R2/R1(V1'-V2');

V1' = R'I + V1 = R'/R(V1 - V2) + V1

V2' = R'I + V1 = R'/R(V1 - V2) + V2;

V0 = (R2/R1)[(2R'/R(V2-V1) + (V2-V1)] = (R2/R1)[(1+2R'/R)(V2-V1)]

- ✓ In a number of industrial and consumer applications, one is required to measure and control physical quantities.

- ✓ Some typical examples are measurement and control of temperature, humidity, light intensity, water flow etc. these physical quantities are usually measured with help of transducers.

- $\checkmark$  The output of transducer has to be amplified so that it can drive the indicator or display system.

- $\checkmark$  This function is performed by an instrumentation amplifier.

- $\checkmark$  The important features of an instrumentation amplifier are

- 1. High gain accuracy

- 2. High CMRR

- 3. High gain stability with low temperature coefficient

- 4. Low output impedance

- ✓ There are specially designed op-amps such as  $\mu$ A725 to meet the above stated requirements of a good instrumentation amplifier.

- ✓ The op-amp A1 and A2 have differential input voltage as zero. For V1=V2, that is, under common mode condition, the voltage across R will be zero. As no current flows through R and R' the non-inverting amplifier.

- ✓ A1 acts as voltage follower, so its output V2<sup>'</sup>=V2. Similarly op-amp A2 acts as voltage follower having output V1<sup>'</sup>=V1. However, if V1≠V2, current flows in R and R<sup>'</sup>, and (V2<sup>'</sup>-V1<sup>'</sup>)> (V2- V1). Therefore, this circuit has differential gain and CMRR more compared to the single opamp circuit.

- ✓ The difference gain of this instrumentation amplifier R, however should never be made zero, as this will make the gain infinity.

- ✓ To avoid such a situation, in a practical circuit, a fixed resistance in series with a potentiometer is used in place of R.

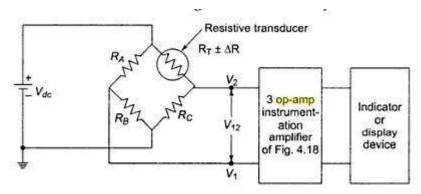

✓ Figure shows a differential instrumentation amplifier using Transducer Bridge.

- ✓ The circuit uses a resistive transducer whose resistance changes as a function of the physical quantity to

- $\checkmark$  be measured.

- ✓ The bridge is initially balanced by a dc supply voltage Vdc so that V1=V2.

- ✓ As the physical quantity changes, the resistance RT of the transducer also changes, causing an unbalance in the bridge (V1≠V2).

- ✓ This differential voltage now gets amplified by the three opamp differential instrumentation amplifier.

$R_B(V_{dc})/(R_B+R_A) = R_C V_{dc}/(R_C+R_T)$

# Applications of instrumentation amplifier with the transducer bridge:

- ✓ temperature indicator,

- $\checkmark$  temperature controller and

- ✓ light intensity meter

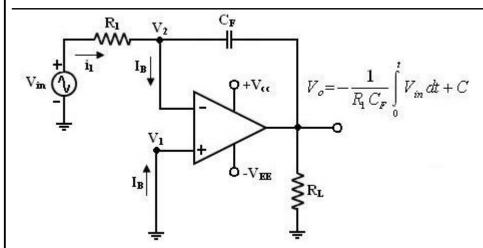

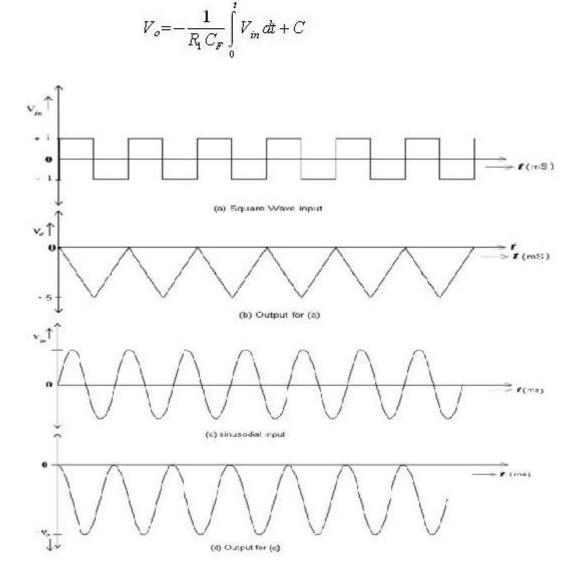

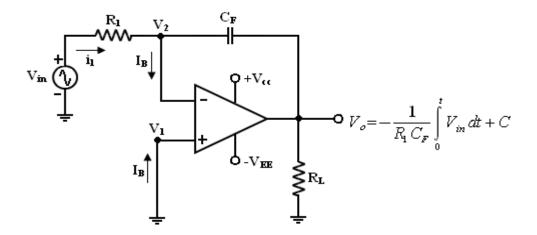

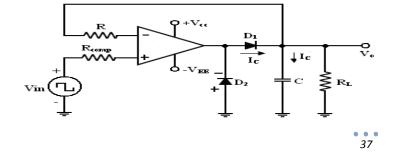

# Integrator:

Q. Explain the circuit that provides an output voltage which is proportional to the time integral of the input. [Nov/Dec 2021][Nov/Dec 2022]

Draw the circuit of integrator using opamp. Explain the working. (Nov 2009)

- ✓ A circuit in which the output voltage is the integral of the input voltage is the integrator or Integration Amplifier.

- $\checkmark$  The expression for the output voltage V0 can be obtained by KVL eqn. at node V2.

$$i_1 = I_B + i_f$$

Since  $I_B$  is negligible small,  $i_1 = i_F$

$\checkmark$  Relation between current through and voltage across the capacitor is

$i_{C}(t) = C dv_{c}(t)/dt$

$\checkmark$  The output voltage can be obtained by integrating both sides with respect to time

. . .

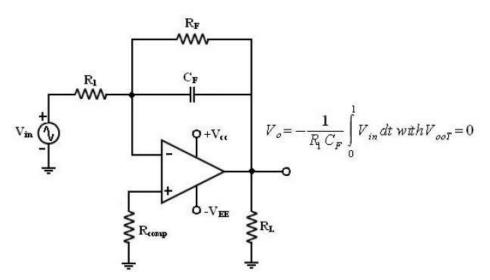

# **Practical Integrator:**

- ✓ Practical Integrator reduce the error voltage at the output, a resistor RF is connected across the feedback capacitor CF.

- ✓ Thus RF limits the low frequency gain and hence minimizes the variations in the output voltages. The frequency response of the basic integrator, shown from this fb is the frequency at which the gain is dB and is given by

$$f_b = \frac{1}{2\pi R_1 C_F}$$

10

- ✓ Both the stability and low frequency roll-off problems can be corrected by the addition of a resistor RF in the practical integrator.

- Stability refers to a constant gain as frequency of an input signal is varied over a certain range.

- Low frequency -> refers to the rate of decrease in gain roll off at lower frequencies.

- $\checkmark$  The gain limiting frequency fa is given by

$$j_a = \frac{1}{2\pi R_1 C_F}$$

- ✓ The value of fa and R1 CF and RF CF values should be selected such that fa<fb.

- ✓ The input signal will be integrated properly if the time period T of the signal is larger than or equal to RF CF,

$$f_b = \frac{1}{2\pi R_F C_F}$$

Uses:

Most commonly used in

- Analog computers

- ADC

- Signal wave shaping circuits.

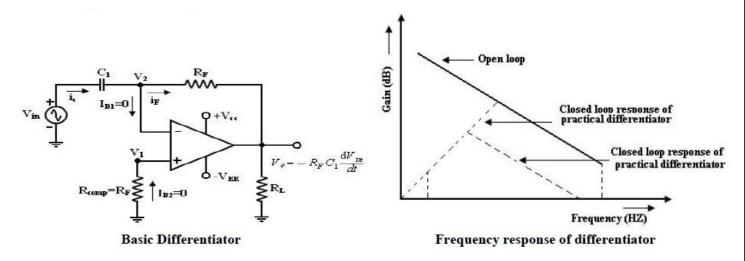

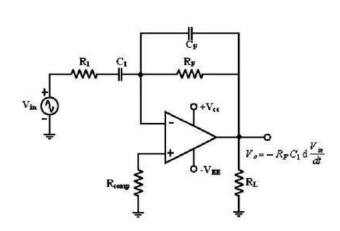

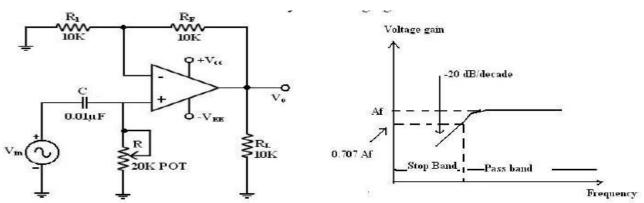

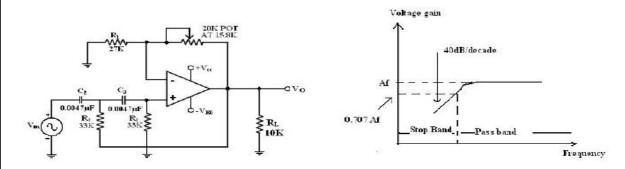

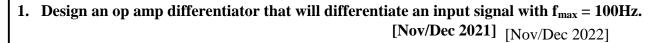

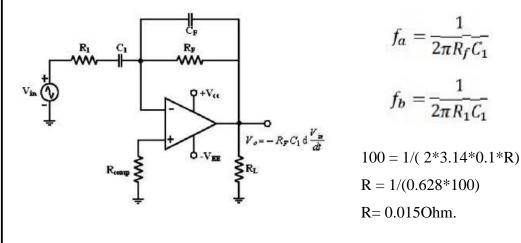

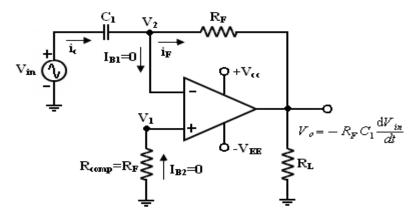

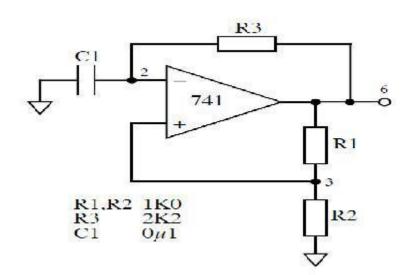

#### **Differentiator:**

Draw the circuit of differentiator using op-amp. Explain the working. (Nov 2009) Explain the circuit that performs the mathematical operation of differentiation. Draw its output wave form. [Nov/Dec 2021]

- ✓ The circuit performs the mathematical operation of differentiation (i.e.) the output waveform is the derivative of the input waveform.

- ✓ Since the differentiator performs the reverse of the integrator function. Thus the output V0 is equal to RF C1 times the negative rate of change of the input voltage Vin with time.

- $\checkmark$  The negative sign indicates a 180 phase shift of the output waveform V0 with respect to the input signal.

- ✓ The below circuit will not do this because it has some practical problems. The gain of the circuit (RF /XC1) R with R in frequency at a rate of 20dB/decade.

- ✓ This makes the circuit unstable. Also input impedance XC1s with R in frequency which makes the circuit very susceptible to high frequency noise.

✓ The output voltage can be obtained by differentiating input voltage with respect to time

$Vo_{(t)} = -RfC1dvin(t)/dt$

**Practical Differentiator:**

$$f_a = \frac{1}{2\pi R_f C_1}$$

$$f_b = \frac{1}{2\pi R_1 C_1}$$

A workable differentiator can be designed by implementing the following steps.

1. Select  $f_a$  equal to the highest frequency of the input signal to be differentiated then assuming a value of  $C_1 < 1\mu f$ . Calculate the value of RF.

2. Choose  $f_b = 20f_a$  and calculate the values of  $R_1$  and  $C_F$  so that  $R_1 C_1 = R_F C_F$ .

#### Uses:

It is used in wave shaping circuits to detect high frequency components in an input signal and also as a rate of change and detector in FM modulators.

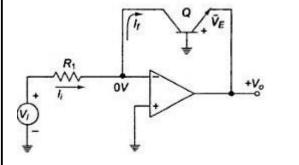

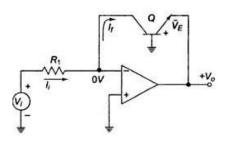

## Log Amplifier:

# Explain the working of log amplifier. (May 2008)

- ✓ A grounded base transistor is placed in the feedback path.

Since the collector is placed in the feedback path.

- ✓ Since the collector is held at virtual ground and the base is also grounded, the transistor's voltage-current relationship becomes that of a diode and is given by,

$$l_E = l_s \left[ e^{q \bar{V}_{\frac{BE}{kT}}} - 1 \right]$$

since  $I_c = I_E$  for a grounded base transistor  $I_C = I_S e^{kT}$

Is=emitter saturation current  $\approx$ 10-13A

k=Boltzmann's constant T=absolute temperature (in o K)

$$V_o = -\frac{kT}{q} ln \left(\frac{V_i}{R_1 I_S}\right) = -\frac{kT}{q} ln \left(\frac{V_i}{V_R}\right)$$

where Vref =R1Is

The output voltage is thus proportional to the logarithm of input voltage.

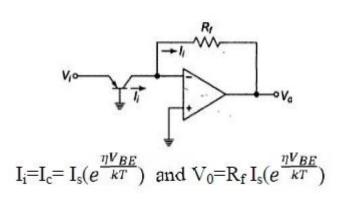

## **Antilog Amplifier**

Explain the working of anti-log amplifier. (May 2005, Dec 2018)

- A circuit to convert logarithmically encoded signal to real signals.

- Transistor in inverting input converts input voltage into logarithmically varying currents.

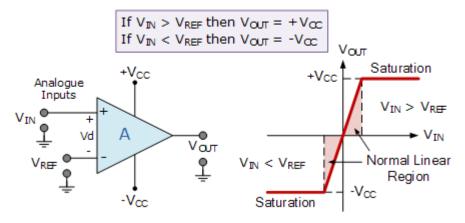

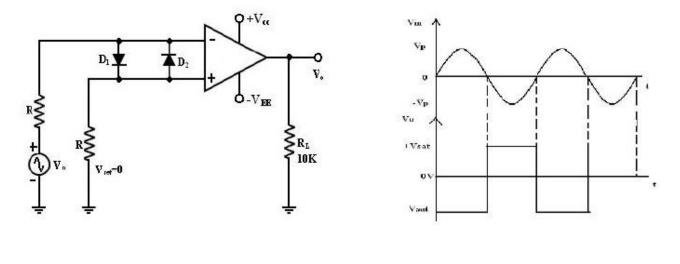

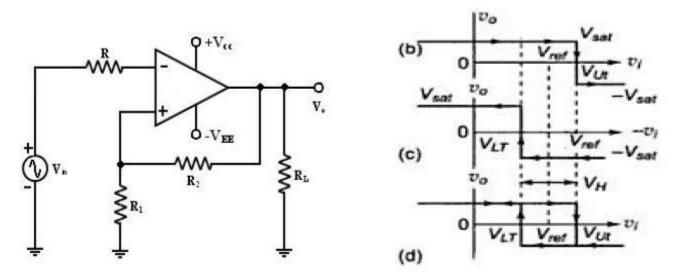

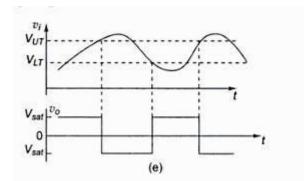

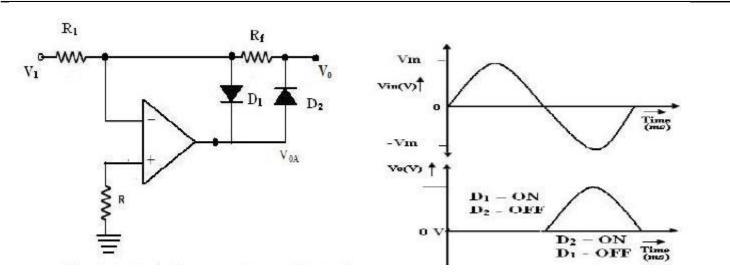

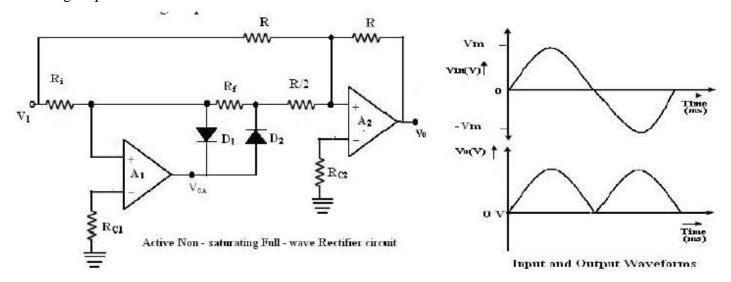

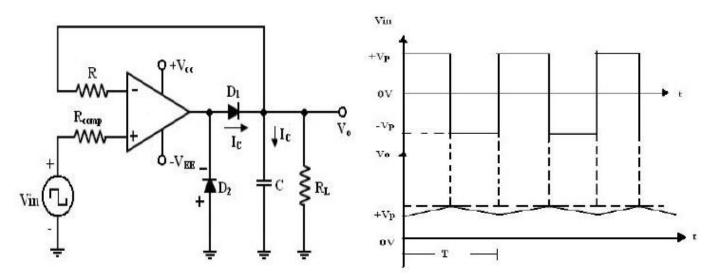

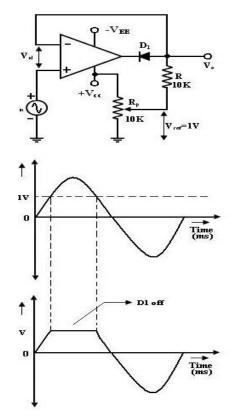

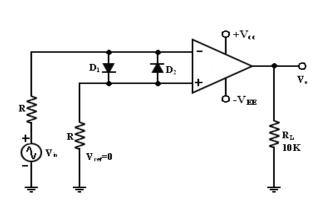

#### Comparator

# Explain the working of inverting and non-inverting comparator using op-amp.[Nov/Dec 2021]

A comparator compares a signal voltage on one input of an op-amp with a known voltage called a reference voltage on the other input. Comparators are used in circuits such as,

- Digital Interfacing

- Schmitt Trigger

- Discriminator

- Voltage level detector and oscillators

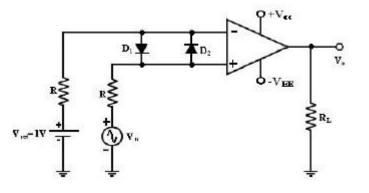

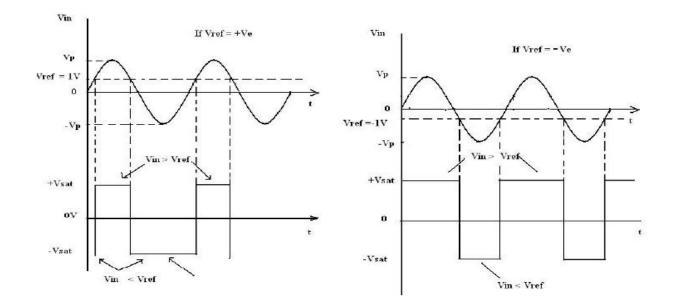

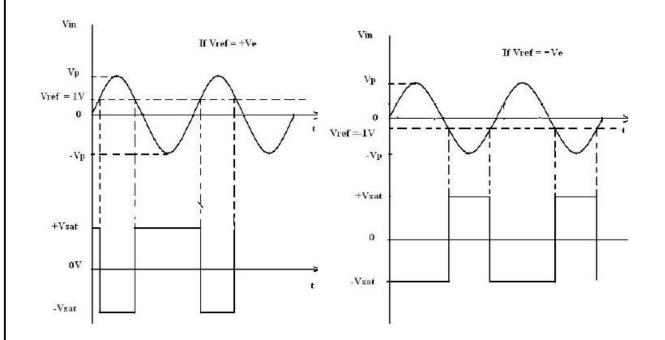

Non-inverting Comparator:

- ✓ A fixed reference voltage Vref of 1 V is applied to the negative terminal and time varying signal voltage Vin is applied to the positive terminal.

- When Vin is less than Vref the output becomes V0 at -Vsat [Vin < Vref =>

V0 (-Vsat)].

✓ When Vin is greater than Vref, the (+) input becomes positive, V0 = +Vsat.

[Vin > Vref => V0 (+Vsat)]. Thus the V0 changes from one saturation level to another.

- ✓ The diodes D1 and D2 protect the op-amp from damage due to the excessive input voltage Vin. Because of these diodes, the difference input voltage Vid of the op-amp diodes are called clamp diodes.

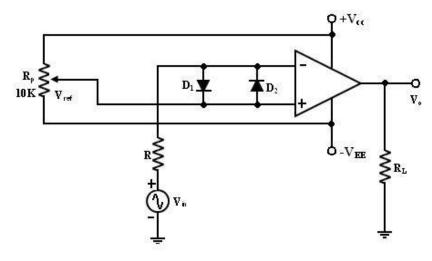

- ✓ The resistance R in series with Vin is used to limit the current through D1 and D2. To reduce offset problems, a resistance Rcomp = R is connected between the (-ve) input and Vref.

#### **Inverting Comparator:**